# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **Cautions**

Keep safety first in your circuit designs!

- Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

- Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation

product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any

other rights, belonging to Renesas Technology Corporation or a third party.

- Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors.

- Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these

materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

# H8/3714 Series

HD6433712 HD6433713 HD6433714, HD6473714

Hardware Manual

# **Preface**

The H8/300L Series of single-chip microcomputers has the high-speed H8/300L CPU at its core, with many necessary peripheral functions on-chip. The H8/300L CPU instruction set is compatible with the H8/300 CPU, and is ideal for realtime control.

The H8/3714 Series has a system-on-a-chip architecture that includes such peripheral functions as a vacuum fluorescent display controller/driver, five timers, a 14-bit PWM, a two-channel serial communication interface, and an A/D converter. It also has high-voltage pins capable of directly driving a vacuum fluorescent display, making it ideal for use in systems employing this type of display.

This manual describes the hardware of the H8/3714 Series. For details on the instruction set, refer to the H8/300L Series Programming Manual.

# Contents

| Section 1 |         | Overview                             | 1  |

|-----------|---------|--------------------------------------|----|

| 1.1       | Overv   | iew                                  | 1  |

| 1.2       | Interna | al Block Diagram                     | 5  |

| 1.3       | Pin Aı  | rangement and Functions              | 6  |

|           | 1.3.1   | Pin Arrangement                      | 6  |

|           | 1.3.2   | Pin Functions                        | 8  |

| Section   | on 2    | CPU                                  | 15 |

| 2.1       | Overv   | iew                                  | 15 |

|           | 2.1.1   | Features                             | 15 |

|           | 2.1.2   | Address Space                        | 16 |

|           | 2.1.3   | Register Configuration               | 17 |

| 2.2       | Regist  | er Descriptions                      | 18 |

|           | 2.2.1   | General Registers                    | 18 |

|           | 2.2.2   | Control Registers                    | 18 |

|           | 2.2.3   | Initial Register Values              | 20 |

| 2.3       | Data F  | Formats                              | 20 |

|           | 2.3.1   | Data Formats in General Registers    | 21 |

|           | 2.3.2   | Memory Data Formats                  | 22 |

| 2.4       | Addre   | ssing Modes                          | 23 |

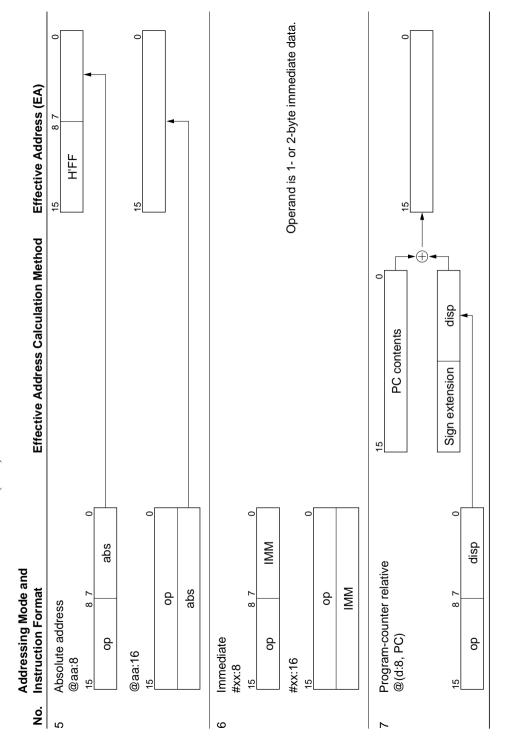

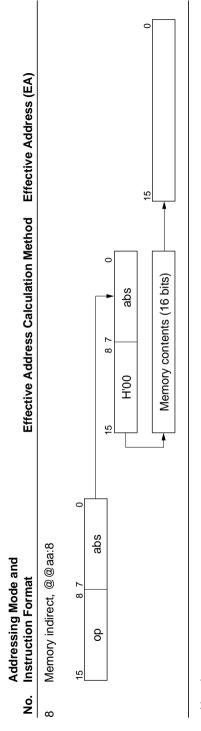

|           | 2.4.1   | Addressing Modes                     | 23 |

|           | 2.4.2   | Effective Address Calculation        | 25 |

| 2.5       | Instruc | ction Set                            | 29 |

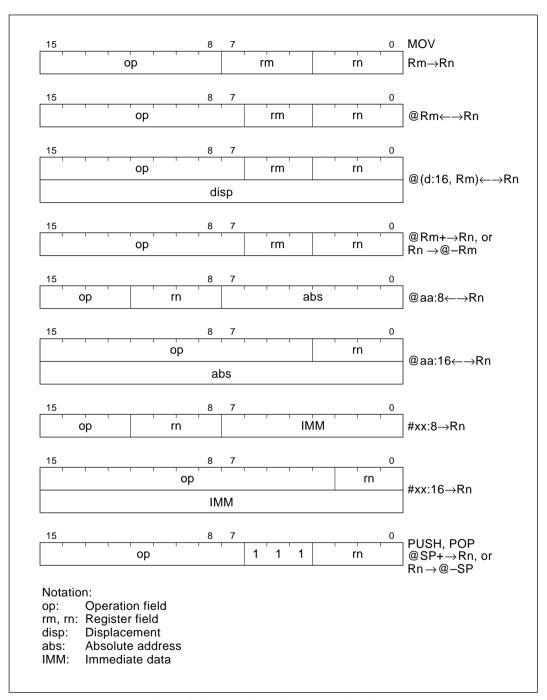

|           | 2.5.1   | Data Transfer Instructions           | 31 |

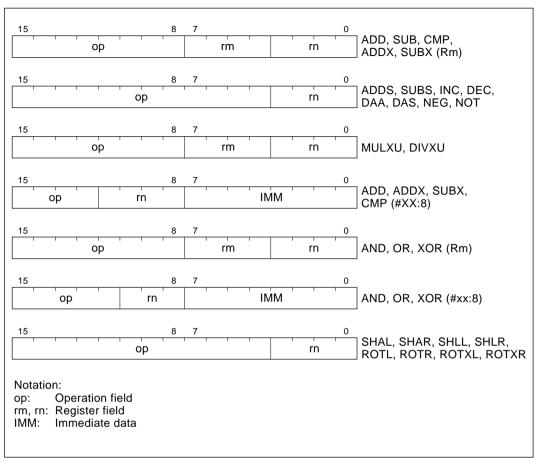

|           | 2.5.2   | Arithmetic Operations                | 33 |

|           | 2.5.3   | Logic Operations                     | 34 |

|           | 2.5.4   | Shift Operations                     | 34 |

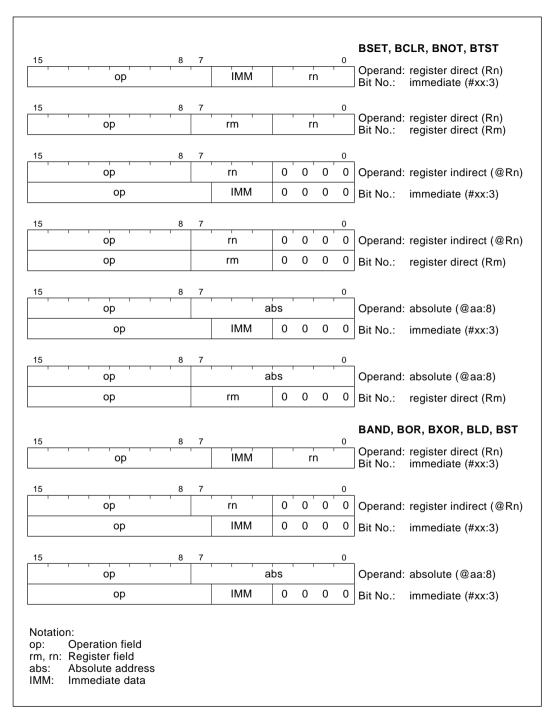

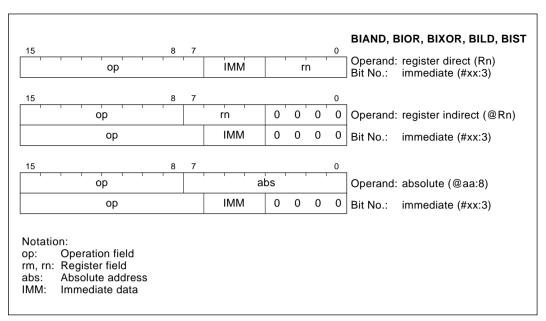

|           | 2.5.5   | Bit Manipulations                    | 36 |

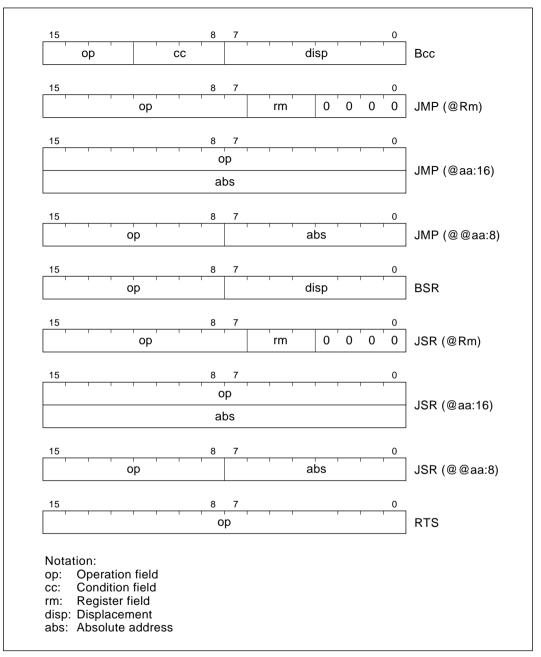

|           | 2.5.6   | Branching Instructions               | 40 |

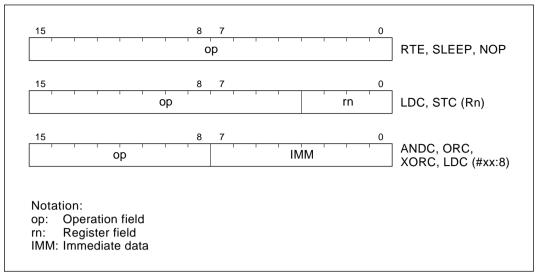

|           | 2.5.7   | System Control Instructions          | 42 |

|           | 2.5.8   | Block Data Transfer Instruction      | 43 |

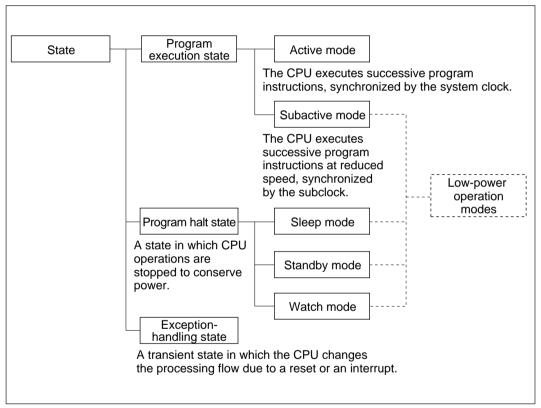

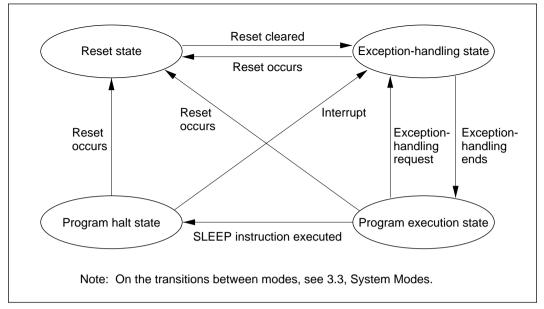

| 2.6       | CPU S   | States                               | 45 |

|           | 2.6.1   | Overview                             | 45 |

|           | 2.6.2   | Program Execution State              | 46 |

|           | 2.6.3   | Program Halt State                   | 46 |

|           | 2.6.4   | Exception-Handling State             | 46 |

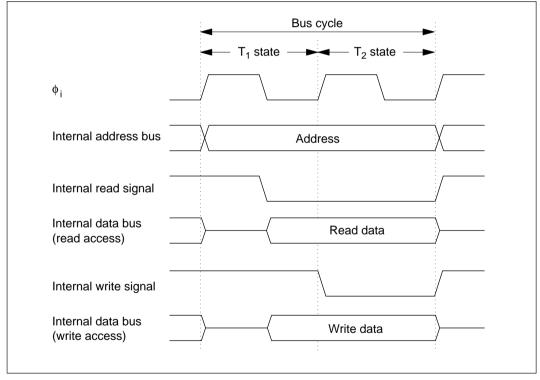

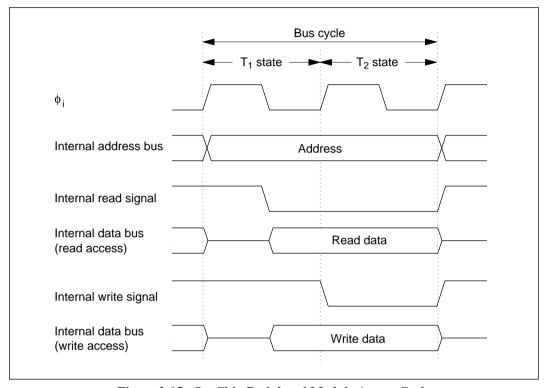

| 2.7       | Basic   | Operation Timing                     | 47 |

|           | 2.7.1   | Access to On-Chip Memory (RAM, ROM)  | 47 |

|           | 2.7.2   | Access to On-Chip Peripheral Modules | 48 |

| 2.8   | Applic | cation Notes                                  | 49 |  |

|-------|--------|-----------------------------------------------|----|--|

|       | 2.8.1  | Notes on Data Access                          | 49 |  |

|       | 2.8.2  | Notes on Bit Manipulation                     | 51 |  |

| Secti | on 3   | System Control                                | 55 |  |

| 3.1   | Overv  | iew                                           | 55 |  |

| 3.2   | Excep  | tion Handling                                 | 55 |  |

|       | 3.2.1  | Reset                                         | 55 |  |

|       | 3.2.2  | Interrupts                                    | 56 |  |

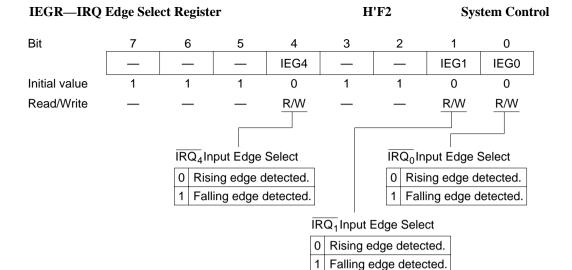

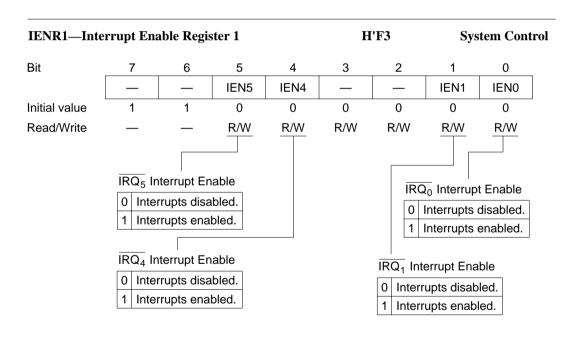

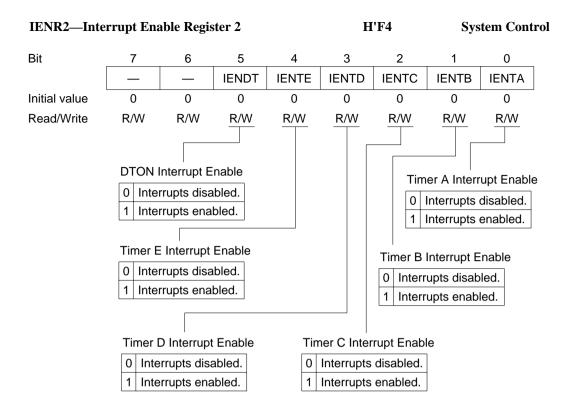

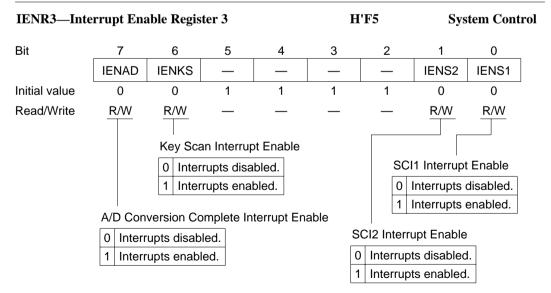

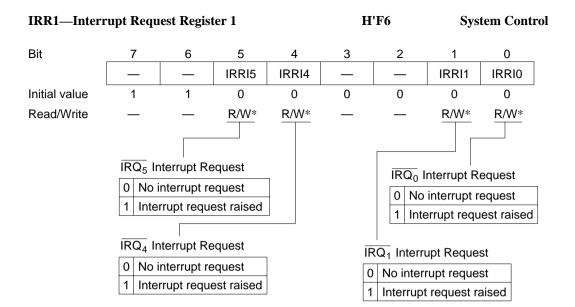

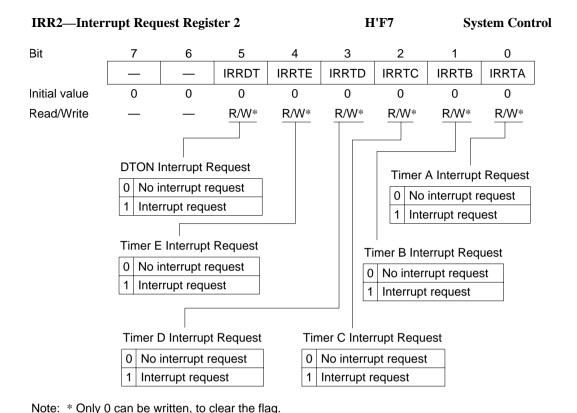

|       | 3.2.3  | Interrupt Control Registers                   | 58 |  |

|       | 3.2.4  | External Interrupts                           | 66 |  |

|       | 3.2.5  | Internal Interrupts                           | 67 |  |

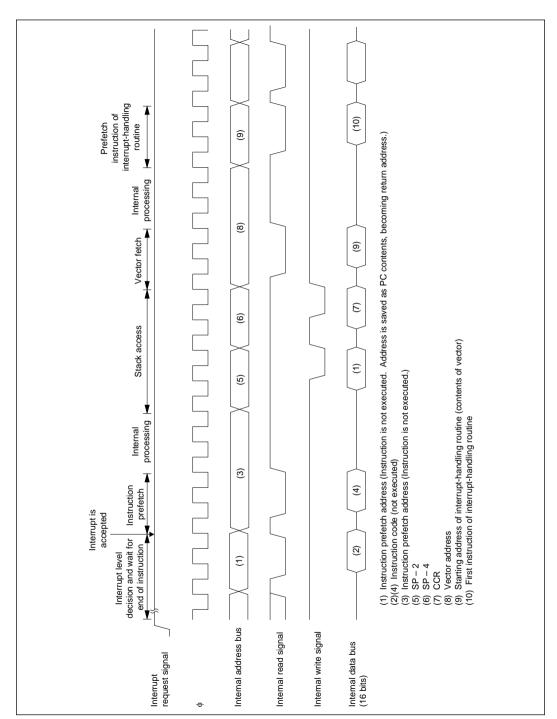

|       | 3.2.6  | Interrupt Operations                          | 67 |  |

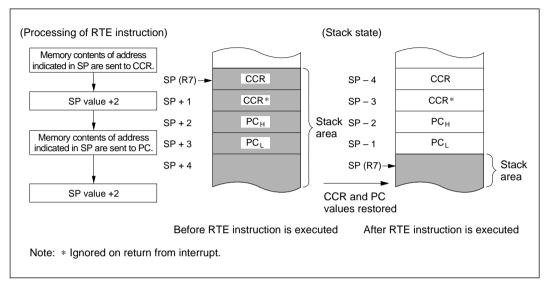

|       | 3.2.7  | Return from an Interrupt                      | 72 |  |

|       | 3.2.8  | Interrupt Response Time                       | 72 |  |

|       | 3.2.9  | Valid Interrupts in Each Mode                 | 73 |  |

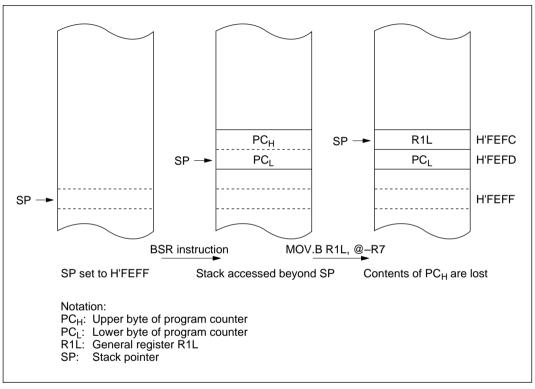

|       | 3.2.10 | Notes on Stack Area Use                       | 74 |  |

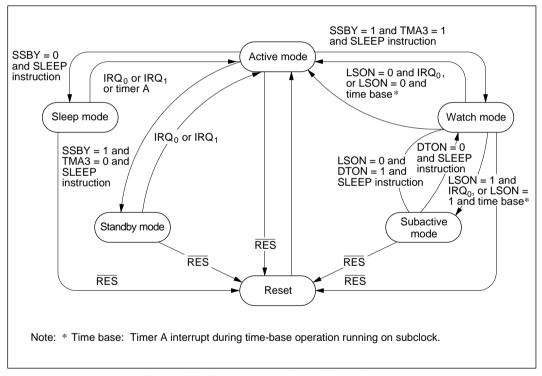

| 3.3   | Systen | n Modes                                       | 75 |  |

|       | 3.3.1  | Active Mode                                   | 76 |  |

|       | 3.3.2  | Low-Power Operation Mode                      | 76 |  |

|       | 3.3.3  | Application Notes                             | 82 |  |

| 3.4   | Systen | n Control Registers                           | 83 |  |

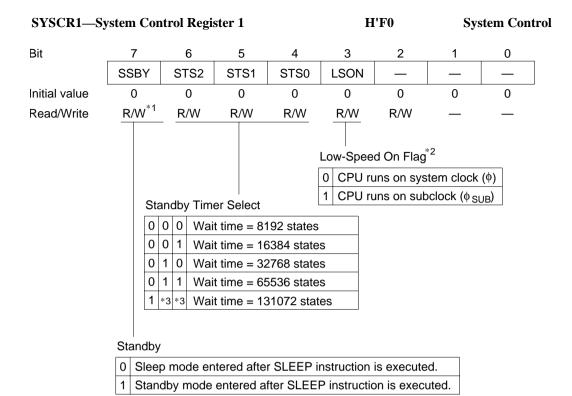

|       | 3.4.1  | System Control Register 1 (SYSCR1)            | 83 |  |

|       | 3.4.2  | System Control Register 2 (SYSCR2)            | 85 |  |

| Secti | on 4   | ROM                                           | 87 |  |

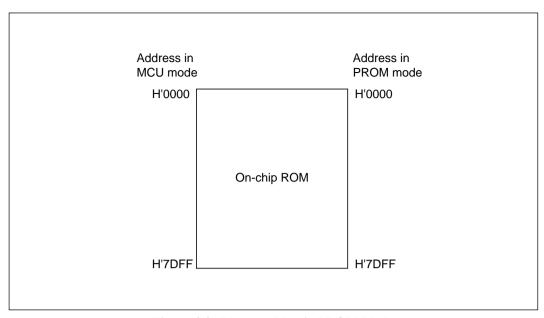

| 4.1   | Overv  | iew                                           |    |  |

|       | 4.1.1  | Block Diagram                                 | 87 |  |

| 4.2   | PROM   | 1 Mode                                        | 88 |  |

|       | 4.2.1  | Selection to PROM Mode                        | 88 |  |

|       | 4.2.2  | Socket Adapter Pin Arrangement and Memory Map | 88 |  |

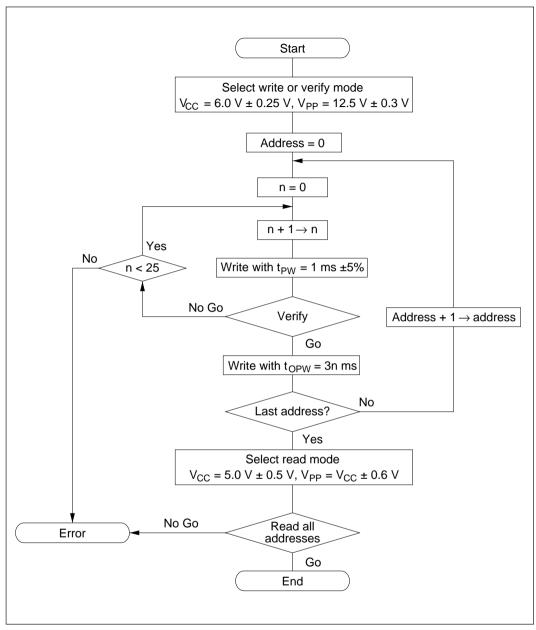

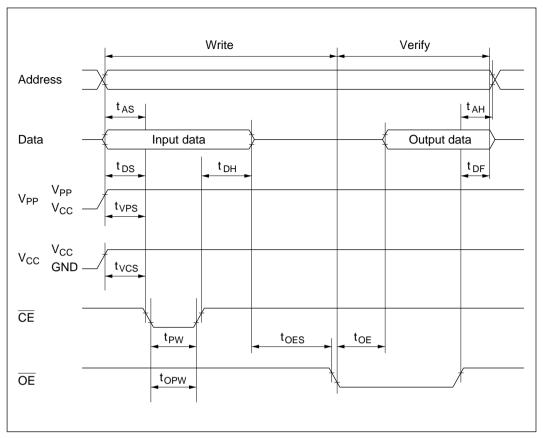

| 4.3   | Progra | ımming                                        | 91 |  |

|       | 4.3.1  |                                               |    |  |

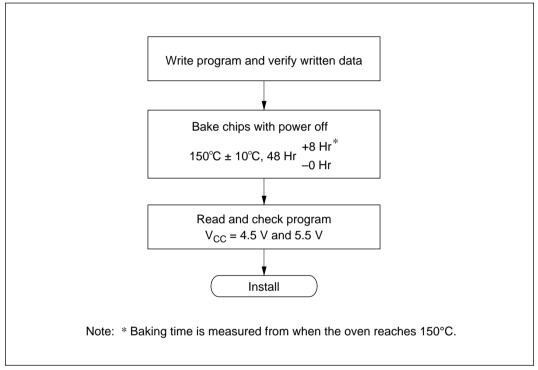

|       | 4.3.2  | Programming Precautions                       |    |  |

|       | 4.3.3  | Reliability of Written Data                   |    |  |

| Secti | on 5   | RAM                                           | 97 |  |

| 5.1   |        | iew                                           | 97 |  |

|       | 5.1.1  | Block Diagram                                 | 97 |  |

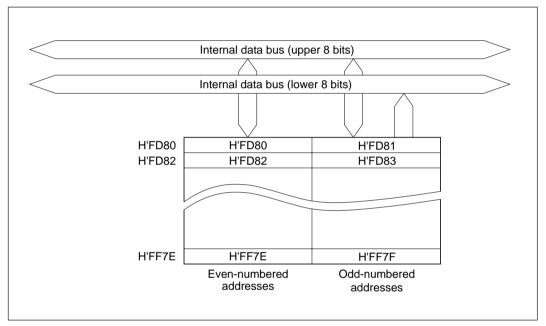

|       | 5.1.2  | Display RAM Area                              | 97 |  |

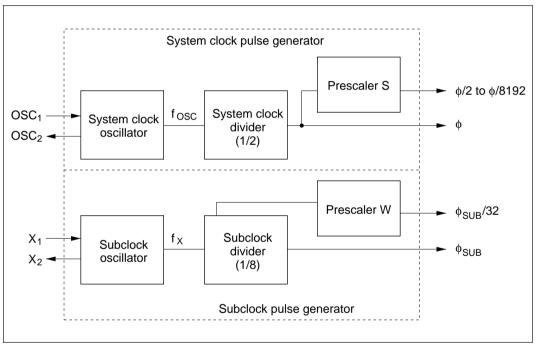

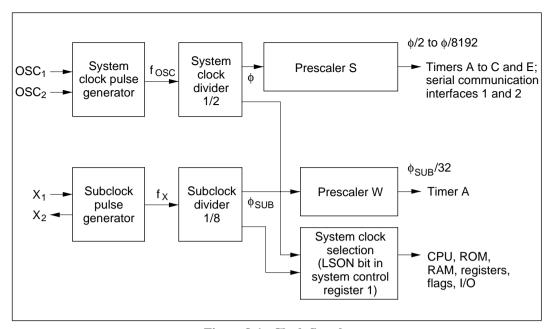

| Section | on 6   | Clock Pulse Generators                 | 99  |

|---------|--------|----------------------------------------|-----|

| 6.1     | Overvi | ew                                     | 99  |

|         | 6.1.1  | Block Diagram                          | 99  |

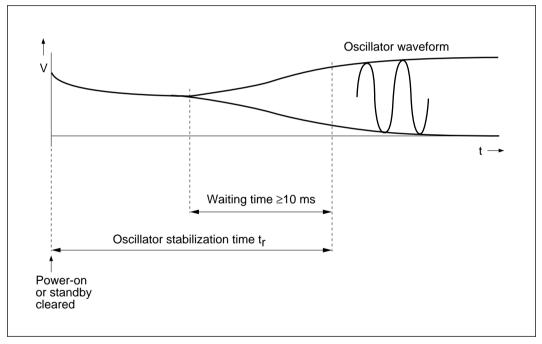

| 6.2     | System | 1 Clock Generator                      | 100 |

| 6.3     | Subclo | ck Generator                           | 103 |

| Section | on 7   | I/O Ports                              | 105 |

| 7.1     | Overvi | ew                                     | 105 |

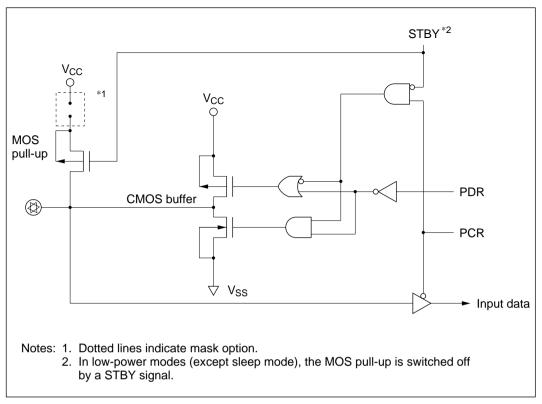

|         | 7.1.1  | Port Types and Mask Options            | 107 |

|         | 7.1.2  | MOS Pull-Up                            | 108 |

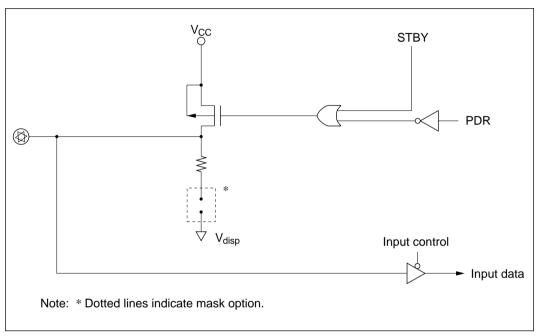

|         | 7.1.3  | MOS Pull-Down                          | 110 |

| 7.2     | Port 0 |                                        | 111 |

|         | 7.2.1  | Overview                               | 111 |

|         | 7.2.2  | Register Configuration and Description | 111 |

|         | 7.2.3  | Pin Functions                          | 112 |

|         | 7.2.4  | Pin States                             | 112 |

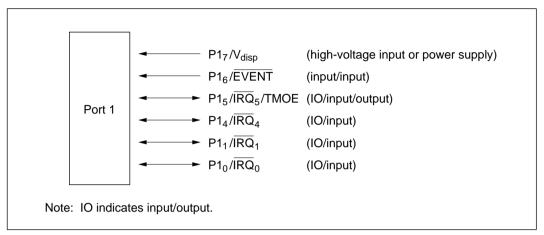

| 7.3     | Port 1 |                                        | 113 |

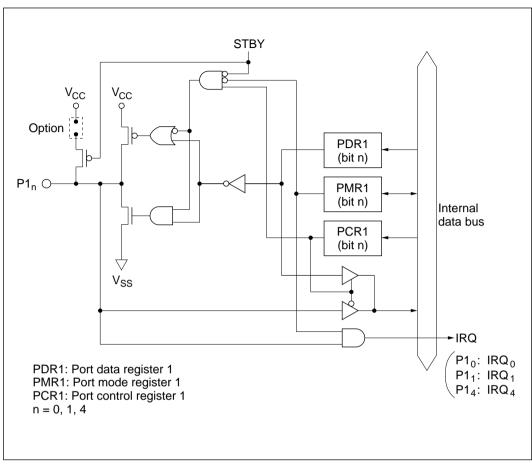

|         | 7.3.1  | Overview                               | 113 |

|         | 7.3.2  | Register Configuration and Description | 113 |

|         | 7.3.3  | Pin Functions                          | 118 |

|         | 7.3.4  | Pin States                             | 119 |

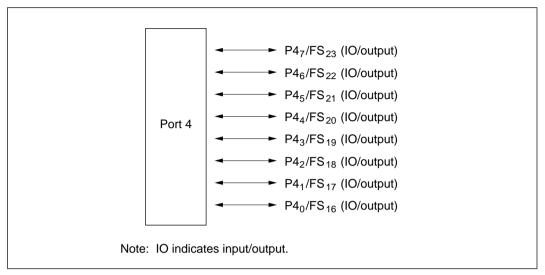

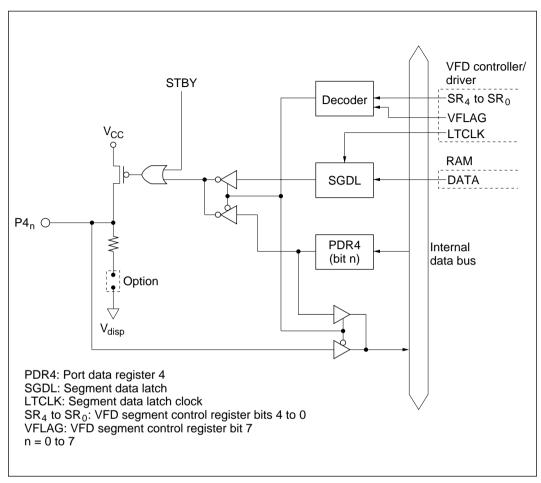

| 7.4     | Port 4 |                                        | 120 |

|         | 7.4.1  | Overview                               | 120 |

|         | 7.4.2  | Register Configuration and Description | 120 |

|         | 7.4.3  | Pin Functions                          | 121 |

|         | 7.4.4  | Pin States                             | 121 |

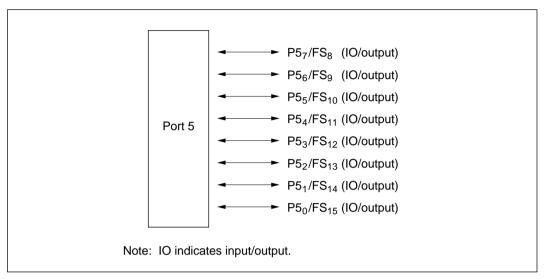

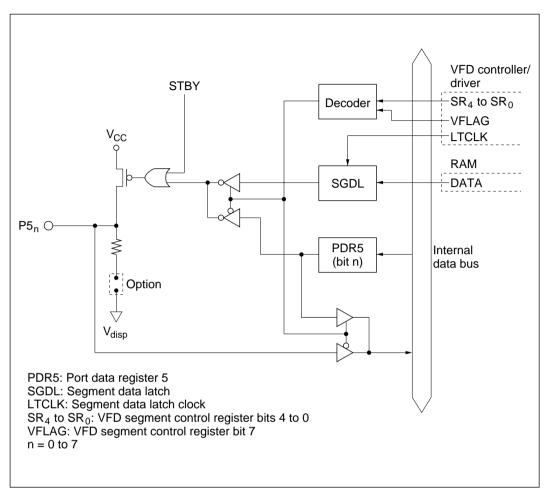

| 7.5     | Port 5 |                                        | 122 |

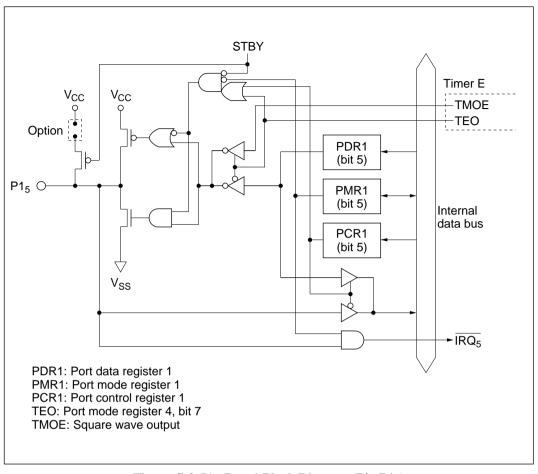

|         | 7.5.1  | Overview                               | 122 |

|         | 7.5.2  | Register Configuration and Description | 122 |

|         | 7.5.3  | Pin Functions                          | 123 |

|         | 7.5.4  | Pin States                             | 123 |

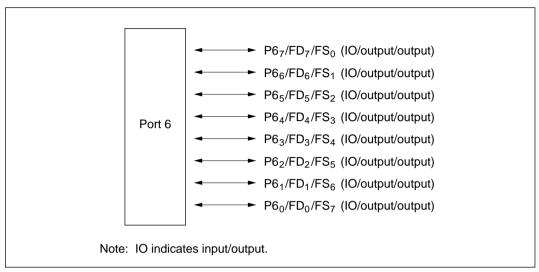

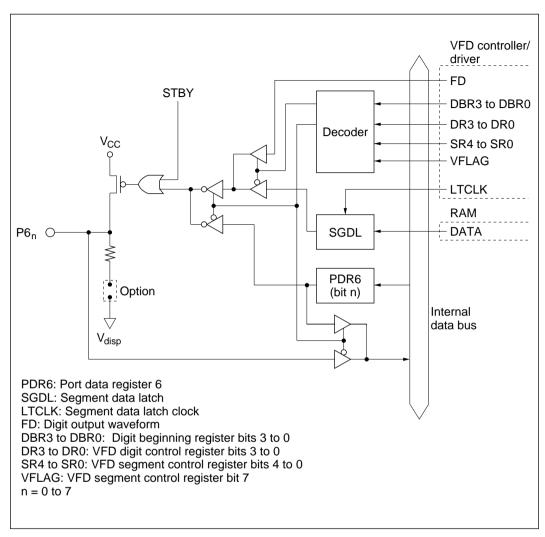

| 7.6     | Port 6 |                                        | 124 |

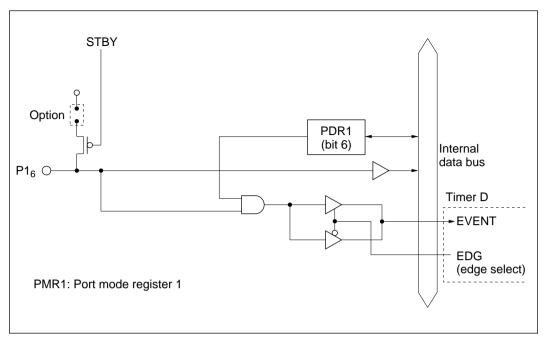

|         | 7.6.1  | Overview                               | 124 |

|         | 7.6.2  | Register Configuration and Description | 124 |

|         | 7.6.3  | Pin Functions                          | 125 |

|         | 7.6.4  | Pin States                             | 125 |

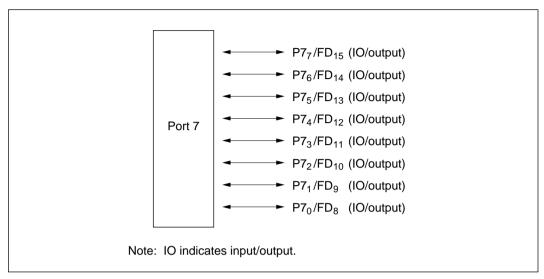

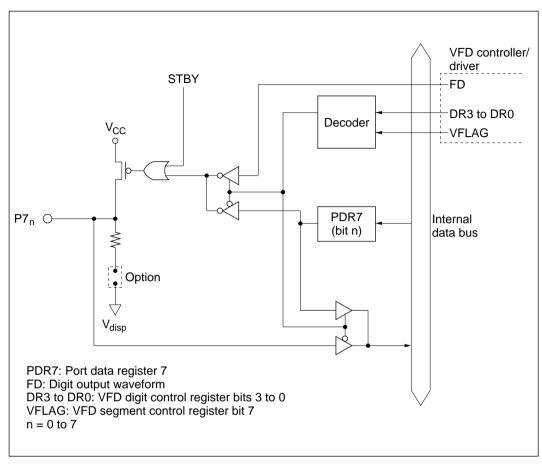

| 7.7     | Port 7 |                                        | 126 |

|         | 7.7.1  | Overview                               | 126 |

|         | 7.7.2  | Register Configuration and Description | 126 |

|         | 7.7.3  | Pin Functions                          |     |

|         | 7.7.4  | Pin States                             | 127 |

|         |        |                                        |     |

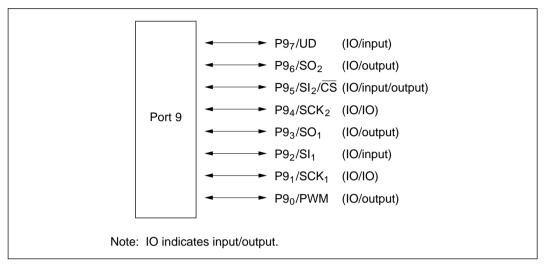

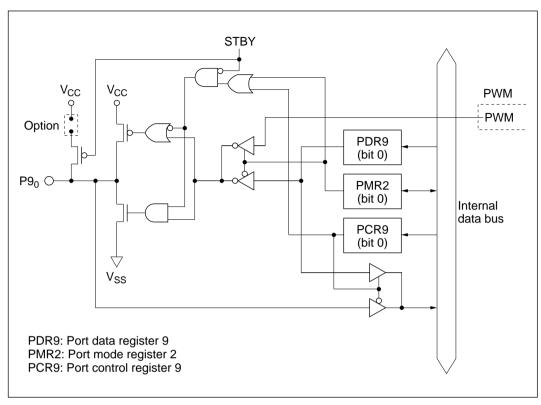

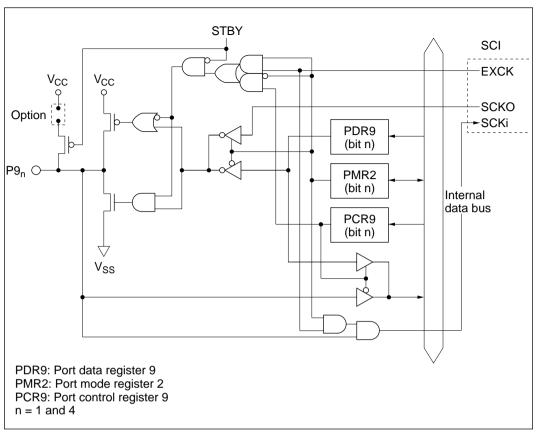

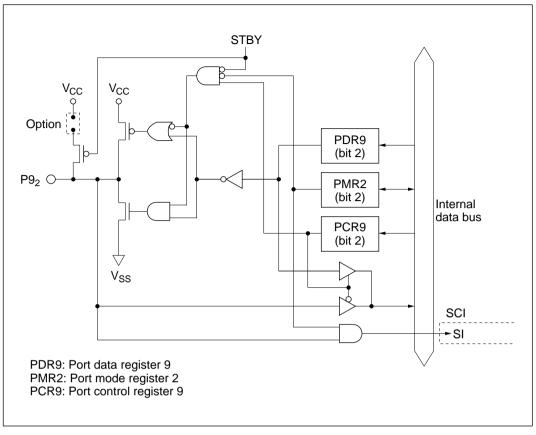

| 7.8     | Port 9  |                                        | 128 |

|---------|---------|----------------------------------------|-----|

|         | 7.8.1   | Overview                               | 128 |

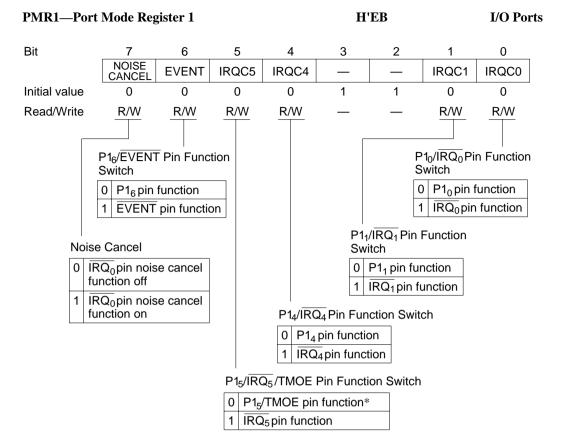

|         | 7.8.2   | Register Configuration and Description | 128 |

|         | 7.8.3   | Pin Functions                          | 132 |

|         | 7.8.4   | Pin States                             | 134 |

| a .     | 0       |                                        |     |

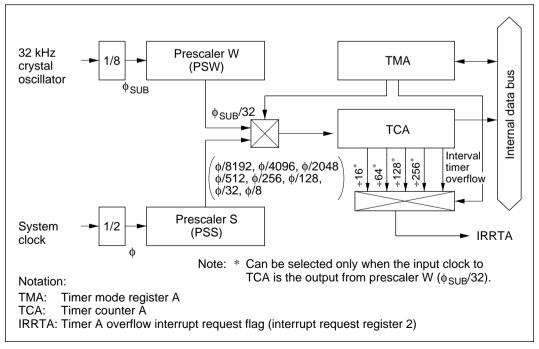

| Section |         | Timers                                 |     |

| 8.1     |         | ew                                     |     |

|         | 8.1.1   | Prescaler Operation                    |     |

| 8.2     |         | A                                      |     |

|         | 8.2.1   | Overview                               |     |

|         | 8.2.2   | Register Descriptions                  |     |

|         | 8.2.3   | Timer Operation                        |     |

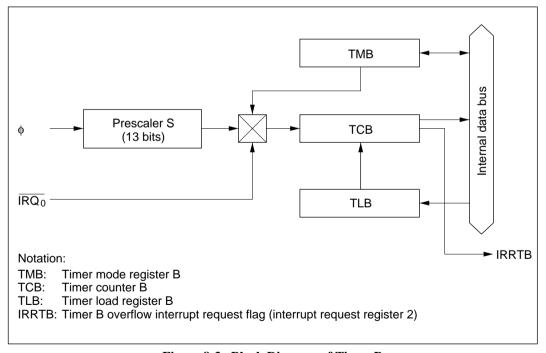

| 8.3     |         | B                                      |     |

|         | 8.3.1   | Overview                               |     |

|         | 8.3.2   | Register Descriptions                  |     |

|         | 8.3.3   | Timer Operation                        |     |

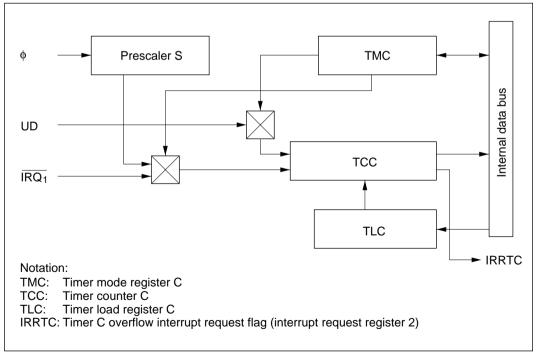

| 8.4     | Timer   | C                                      | 148 |

|         | 8.4.1   | Overview                               | 148 |

|         | 8.4.2   | Register Descriptions                  | 149 |

|         | 8.4.3   | Timer Operation                        | 152 |

| 8.5     | Timer   | D                                      | 154 |

|         | 8.5.1   | Overview                               | 154 |

|         | 8.5.2   | Register Descriptions                  |     |

|         | 8.5.3   | Timer Operation                        | 157 |

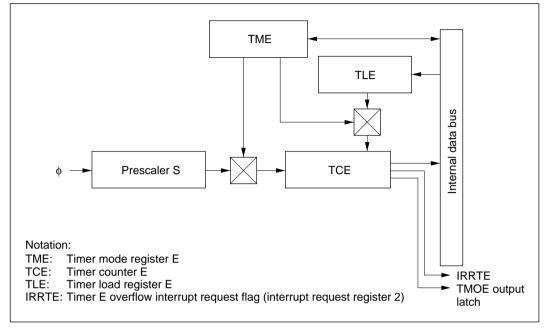

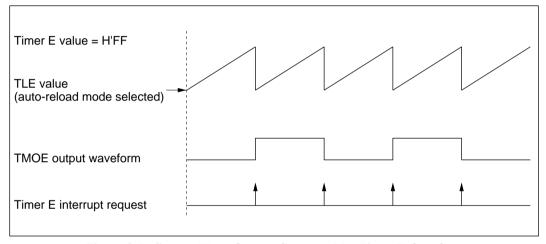

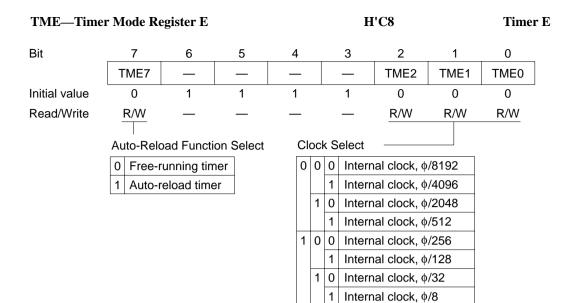

| 8.6     | Timer   | E                                      | 158 |

|         | 8.6.1   | Overview                               | 158 |

|         | 8.6.2   | Register Descriptions                  | 160 |

|         | 8.6.3   | Timer Operation                        | 164 |

| 8.7     | Interru | pts                                    | 167 |

| 8.8     | Applic  | eation Notes                           | 167 |

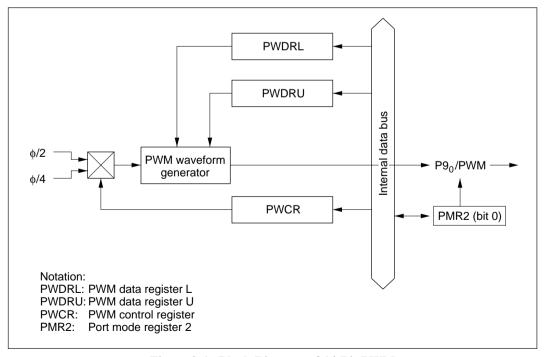

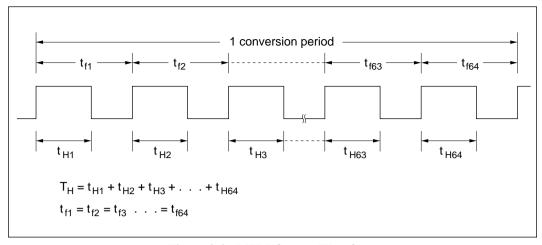

| Section | on 9    | 14-Bit PWM                             | 169 |

| 9.1     |         | ew                                     |     |

| J.1     | 9.1.1   | Features                               |     |

|         | 9.1.2   | Block Diagram                          |     |

|         | 9.1.3   | Pin Configuration                      |     |

|         | 9.1.3   | Register Configuration.                |     |

|         | J.1.T   | Register Configuration                 | 1/0 |

| 9.2     | Regist | er Descriptions                           | 171 |

|---------|--------|-------------------------------------------|-----|

|         | 9.2.1  | PWM Control Register (PWCR)               | 171 |

|         | 9.2.2  | PWM Data Registers U and L (PWDRU, PWDRL) | 172 |

| 9.3     | Operat | tion                                      | 173 |

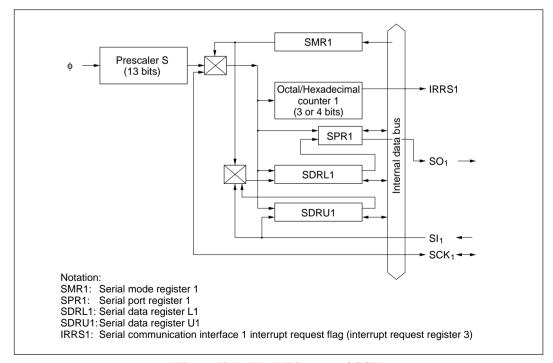

| Section | on 10  | SCI1                                      | 175 |

| 10.1    | Overvi | iew                                       | 175 |

|         | 10.1.1 | Features                                  | 175 |

|         | 10.1.2 | Block Diagram                             | 175 |

|         | 10.1.3 | Pin Configuration                         | 176 |

|         | 10.1.4 | Register Configuration                    | 176 |

| 10.2    | Regist | er Descriptions                           | 177 |

|         | 10.2.1 | Serial Mode Register 1 (SMR1)             | 177 |

|         | 10.2.2 | Serial Data Register U1 (SDRU1)           | 178 |

|         |        | Serial Data Register L1 (SDRL1)           |     |

|         |        | Serial Port Register 1 (SPR1)             |     |

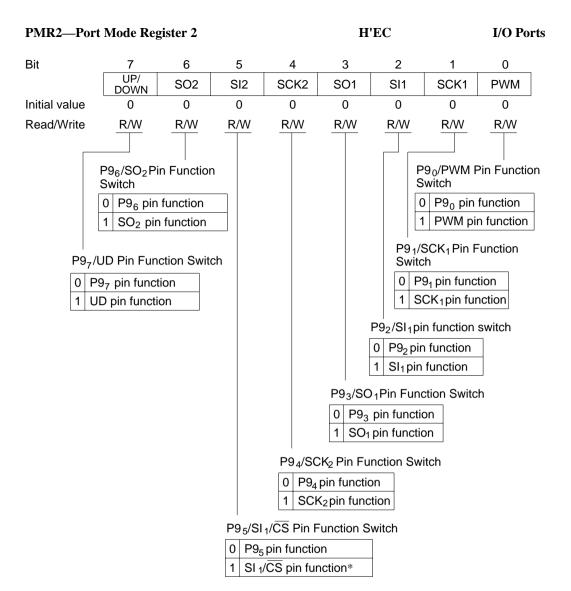

|         |        | Port Mode Register 2 (PMR2)               |     |

|         |        | Port Mode Register 3 (PMR3)               |     |

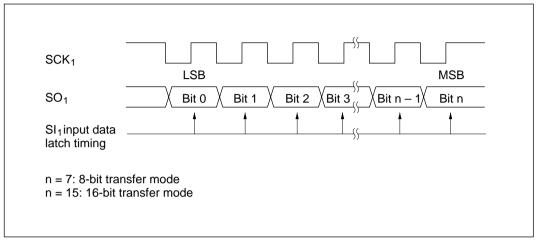

| 10.3    |        | tion                                      |     |

|         | 10.3.1 | Overview                                  | 182 |

|         | 10.3.2 | Data Transfer Format                      | 183 |

|         |        | Clock                                     |     |

|         | 10.3.4 | Data Transmit/Receive                     | 183 |

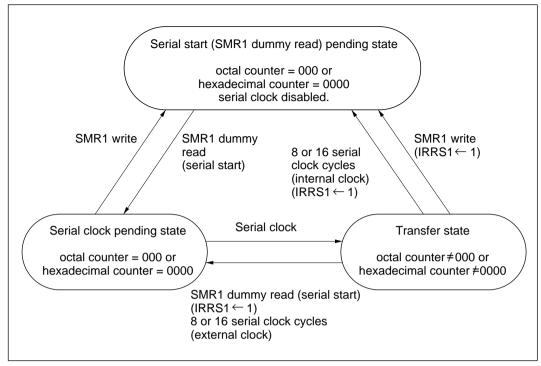

|         |        | SCI1 State Transitions                    |     |

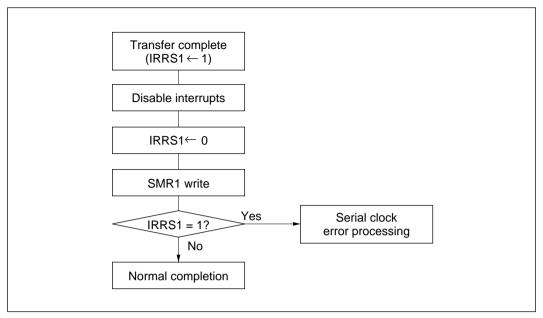

|         |        | Serial Clock Error Detection              |     |

|         |        | Interrupts                                |     |

| Section | on 11  | SCI2                                      | 189 |

| 11.1    |        | iew                                       |     |

|         |        | Features                                  |     |

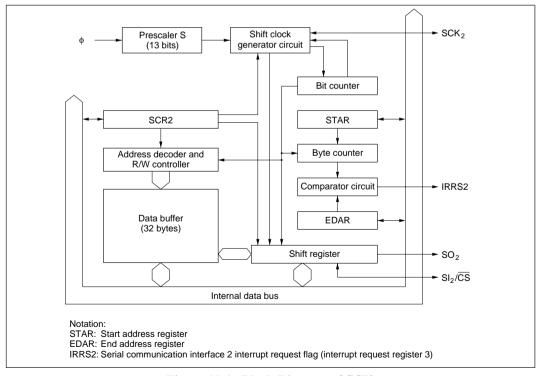

|         |        | Block Diagram                             |     |

|         |        | Pin Configuration.                        |     |

|         |        | Register Configuration                    |     |

| 11.2    |        | er Descriptions                           |     |

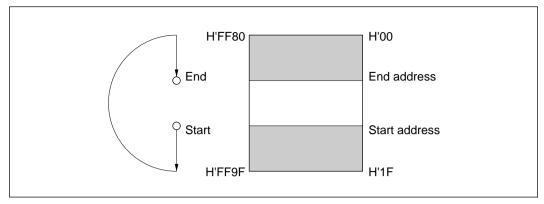

|         | 11.2.1 | Start Address Register (STAR)             | 191 |

|         |        | End Address Register (EDAR)               |     |

|         |        | Serial Control Register 2 (SCR2)          |     |

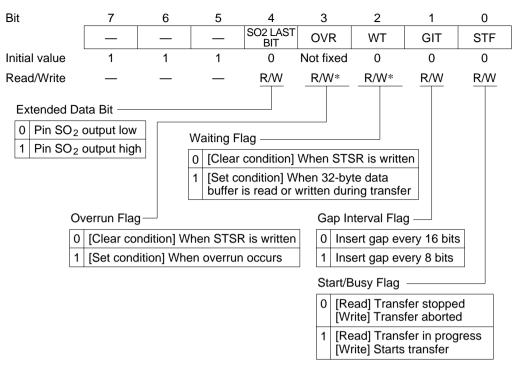

|         |        | Status Register (STSR)                    |     |

|         |        | Port Mode Register 3 (PMR3)               |     |

| 11.3    |        | tion                                      |     |

|         | _      | Overview                                  |     |

|         |        |                                           |     |

|         | 11.3.2 Clock                                           | 198 |

|---------|--------------------------------------------------------|-----|

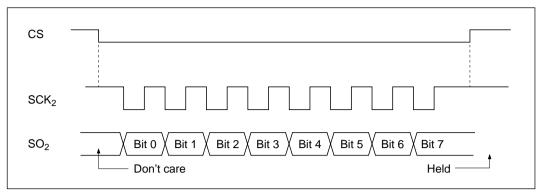

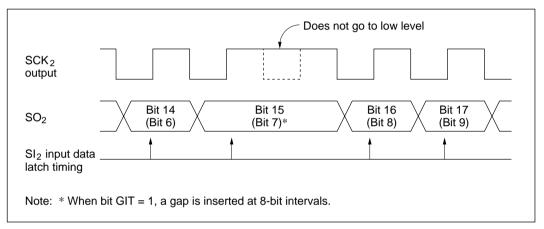

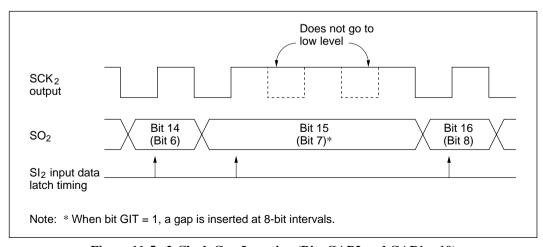

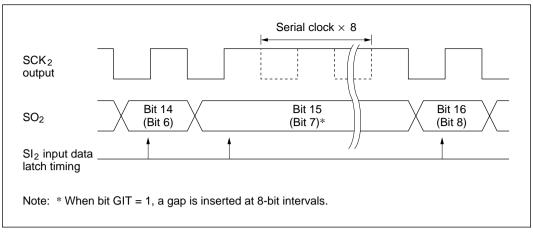

|         | 11.3.3 Data Transfer Format                            | 198 |

|         | 11.3.4 Data Transmit/Receive                           | 200 |

| 11.4    | Interrupts                                             | 202 |

| 11.5    | Application Notes                                      | 202 |

|         |                                                        |     |

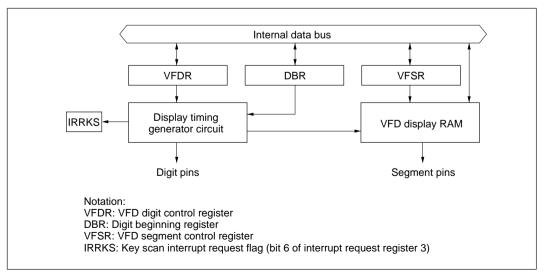

| Section | on 12 VFD Controller/Driver                            | 203 |

| 12.1    | Overview                                               | 203 |

|         | 12.1.1 Features                                        | 203 |

|         | 12.1.2 Block Diagram                                   | 203 |

|         | 12.1.3 Pin Configuration                               | 204 |

|         | 12.1.4 Register Configuration                          | 204 |

| 12.2    | Register Descriptions                                  | 205 |

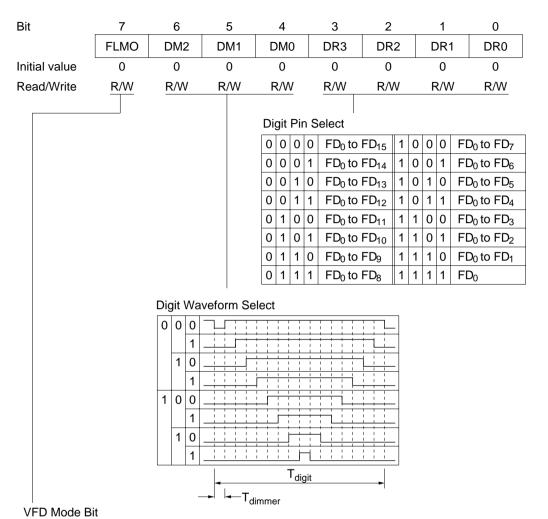

|         | 12.2.1 VFD Digit Control Register (VFDR)               | 205 |

|         | 12.2.2 VFD Segment Control Register (VFSR)             | 208 |

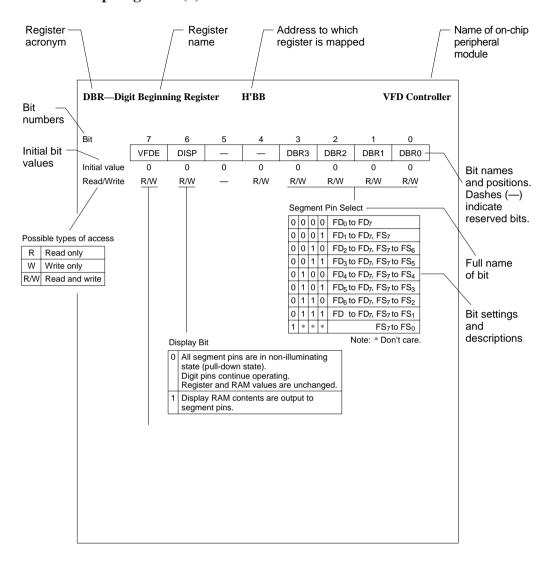

|         | 12.2.3 Digit Beginning Register (DBR)                  | 210 |

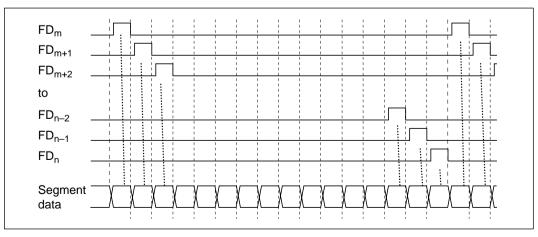

| 12.3    | Operation                                              | 212 |

|         | 12.3.1 Overview                                        | 212 |

|         | 12.3.2 Control Section                                 | 212 |

|         | 12.3.3 RAM Bit Correspondence to Digits/Segments       | 212 |

|         | 12.3.4 Procedure for Starting Operation                | 214 |

| 12.4    | Interrupts                                             | 214 |

| 12.5    | Occurrence of Flicker when VFD Registers are Rewritten | 214 |

|         |                                                        |     |

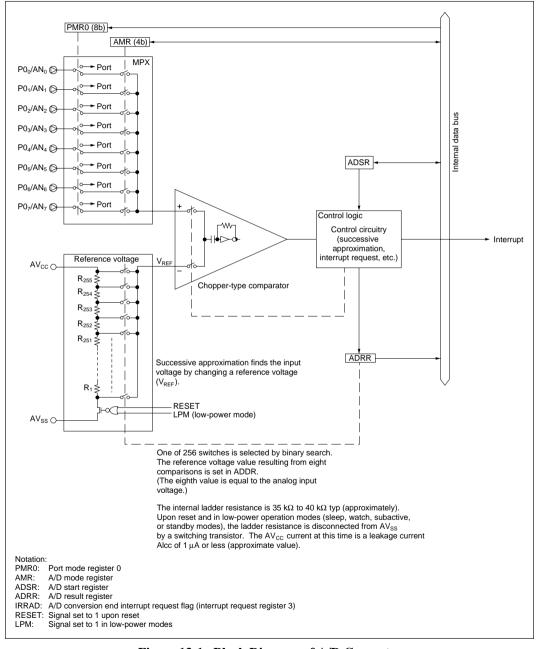

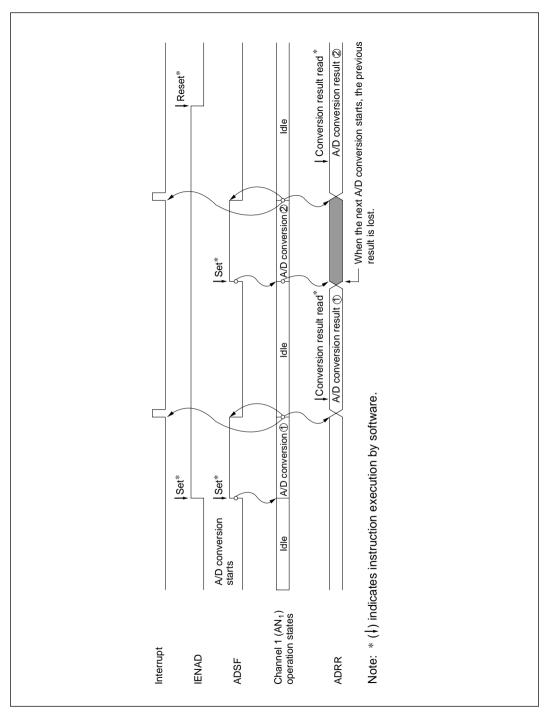

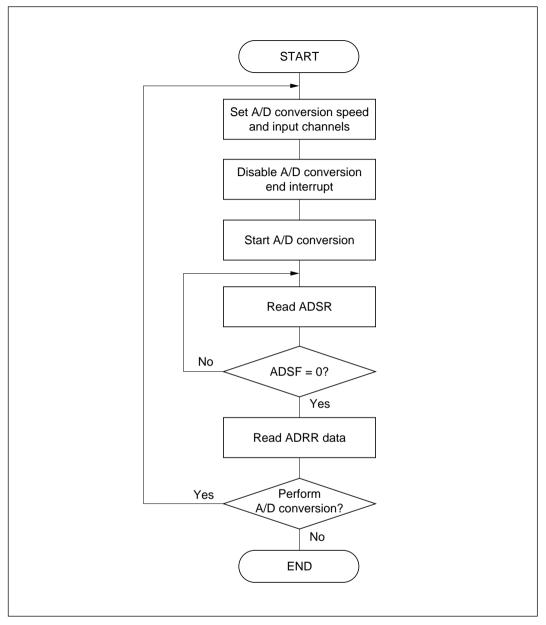

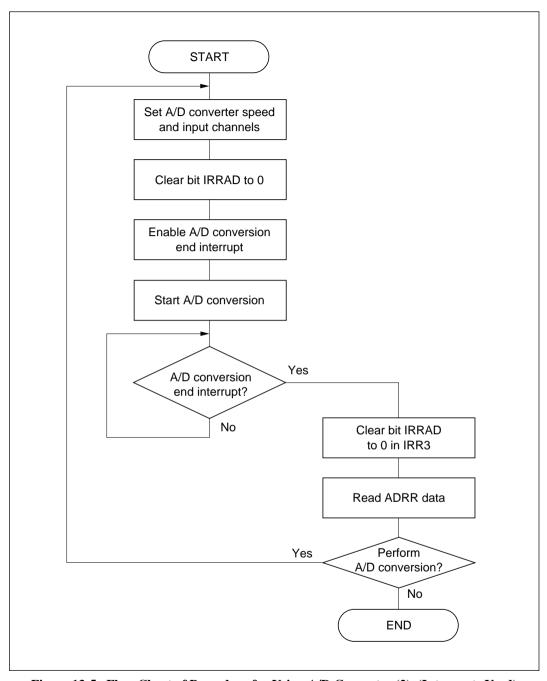

| Section | on 13 A/D Converter                                    | 215 |

| 13.1    | Overview                                               | 215 |

|         | 13.1.1 Features                                        | 215 |

|         | 13.1.2 Block Diagram                                   | 216 |

|         | 13.1.3 Pin Configuration                               | 217 |

|         | 13.1.4 Register Configuration                          | 217 |

| 13.2    | Register Descriptions                                  | 218 |

|         | 13.2.1 A/D Result Register (ADRR)                      | 218 |

|         | 13.2.2 A/D Mode Register (AMR)                         |     |

|         | 13.2.3 A/D Start Register (ADSR)                       | 221 |

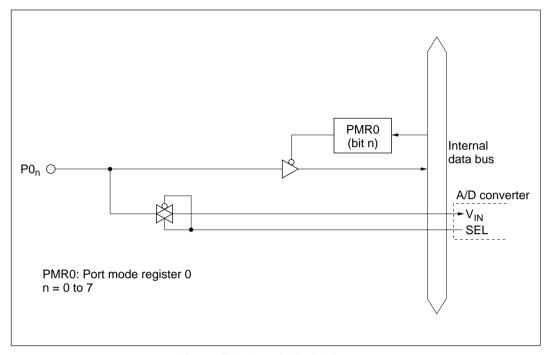

|         | 13.2.4 Port Mode Register 0 (PMR0)                     |     |

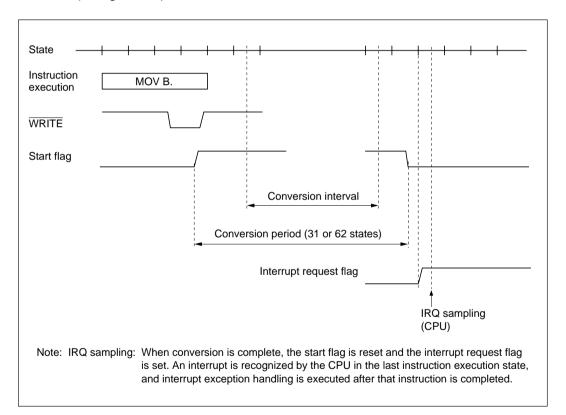

| 13.3    | Operation                                              |     |

| 13.4    | Interrupts                                             |     |

| 13.5    | Typical Use                                            |     |

| 13.6    | Application Notes                                      |     |

|         |                                                        |     |

| Secti    | on 14 Electrical Specifications                                         | 229 |

|----------|-------------------------------------------------------------------------|-----|

| 14.1     | Absolute Maximum Ratings                                                | 229 |

| 14.2     | HD6473714 Electrical Characteristics                                    | 230 |

|          | 14.2.1 HD6473714 DC Characteristics                                     | 230 |

|          | 14.2.2 HD6473714 AC Characteristics                                     | 236 |

|          | 14.2.3 HD6473714 A/D Converter Characteristics                          | 239 |

| 14.3     | HD6433712, HD6433713 and HD6433714 Electrical Characteristics           | 240 |

|          | 14.3.1 HD6433712, HD6433713 and HD6433714 DC Characteristics            | 240 |

|          | 14.3.2 HD6433712, HD6433713 and HD6433714 AC Characteristics            | 246 |

|          | 14.3.3 HD6433712, HD6433713 and HD6433714 A/D Converter Characteristics | 249 |

| 14.4     | Operational Timing                                                      | 250 |

| 14.5     | Differences in Electrical Characteristics between HD6473714 and         |     |

|          | HD6433712/HD6433713/HD6433714                                           | 253 |

| Anne     | endix A CPU Instruction Set                                             | 255 |

| A.1      | Instruction Notation                                                    |     |

| A.2      | Operation Code Map                                                      |     |

| A.3      | Number of States Required for Execution                                 |     |

| <b>A</b> | and's D. On Chin Desistant                                              | 265 |

|          | endix B On-Chip Registers                                               |     |

| B.1      | On-Chip Registers (1)                                                   |     |

| B.2      | On-Chip Registers (2)                                                   | 268 |

| Appe     | endix C I/O Port Block Diagrams                                         |     |

| C.1      | Port 0 Block Diagram                                                    | 295 |

| C.2      | Port 1 Block Diagram                                                    | 296 |

| C.3      | Port 4 Block Diagram                                                    | 299 |

| C.4      | Port 5 Block Diagram                                                    | 300 |

| C.5      | Port 6 Block Diagram                                                    | 301 |

| C.6      | Port 7 Block Diagram                                                    | 302 |

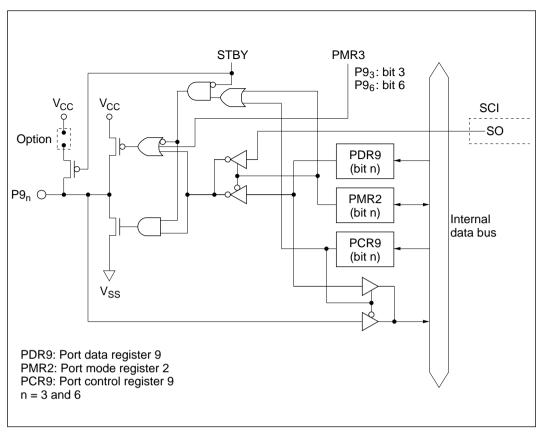

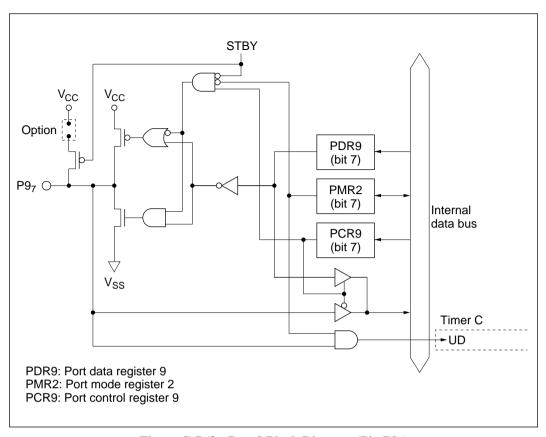

| C.7      | Port 9 Block Diagram                                                    | 303 |

| Арре     | endix D Port States in Each Processing State                            | 309 |

| Арре     | endix E List of Mask Options                                            | 311 |

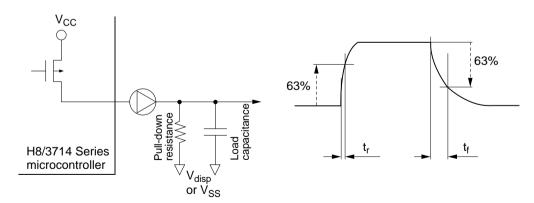

| Арре     | endix F Rise Time and Fall Time of High-Voltage Pins                    | 312 |

| Appe     | endix G Package Dimensions                                              | 313 |

# Section 1 Overview

#### 1.1 Overview

The H8/300L Series is a series of single-chip microcontrollers (MCU: microcomputer unit) built around the high-speed H8/300L CPU and equipped with peripheral system functions on-chip.

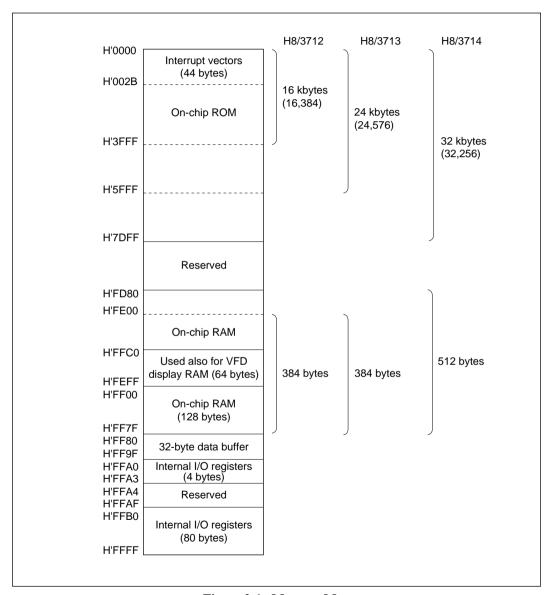

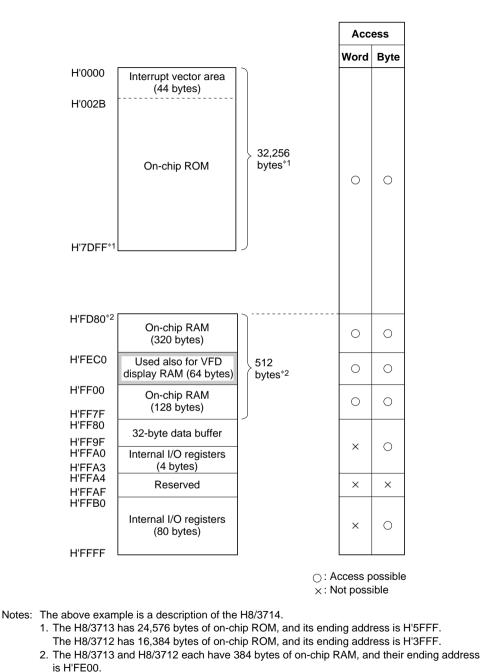

Within the H8/300L Series, the H8/3714 Series microcontrollers are equipped with high-voltage pins. On-chip peripheral functions include a vacuum fluorescent display (VFD) controller/driver, timers, a 14-bit pulse width modulator (digital-to-analog converter), two serial communication interface channels, and an analog-to-digital converter. Together, these functions make the H8/3714 Series ideally suited for embedded control of systems requiring a vacuum fluorescent display. On-chip memory is 16 kbytes of ROM and 384 bytes of RAM in the H8/3712, 24 kbytes of ROM and 384 bytes of RAM in the H8/3713, or 32 kbytes of ROM and 512 bytes of RAM in the H8/3714, providing a choice for systems of different sizes. The ZTAT<sup>TM\*</sup> versions of the H8/3714 come with user-programmable PROM.

Table 1 summarizes the features of the H8/3714 Series.

Note: \* ZTAT (zero turn-around time) is a trademark of Hitachi, Ltd.

**Table 1-1 Features**

| Item   | Description                                                                                                |

|--------|------------------------------------------------------------------------------------------------------------|

| CPU    | General-register architecture                                                                              |

|        | <ul> <li>General registers: Sixteen 8-bit registers (can be used as eight 16-bit<br/>registers)</li> </ul> |

|        | Operating speed                                                                                            |

|        | Max. operating speed: 4.19 MHz                                                                             |

|        | <ul> <li>Add/subtract: 0.5 μs (operating at φ = 4 MHz)</li> </ul>                                          |

|        | • Multiply/divide: 3.5 $\mu$ s (operating at $\phi = 4$ MHz)                                               |

|        | Can run on 32 kHz subclock                                                                                 |

|        | Instruction set compatible with H8/300 CPU                                                                 |

|        | <ul> <li>Instruction length of 2 bytes or 4 bytes</li> </ul>                                               |

|        | Basic arithmetic operations between registers                                                              |

|        | <ul> <li>MOV instruction for data transfer between memory and registers</li> </ul>                         |

|        | Instruction features                                                                                       |

|        | <ul> <li>Multiply (8 bits × 8 bits)</li> </ul>                                                             |

|        | • Divide (16 bits ÷ 8 bits)                                                                                |

|        | Bit accumulator                                                                                            |

|        | Register-indirect designation of bit position                                                              |

| Memory | H8/3714: 32 kbyte ROM, 512 byte RAM                                                                        |

|        | <ul> <li>H8/3713: 24 kbyte ROM, 384 byte RAM</li> </ul>                                                    |

|        | <ul> <li>H8/3712: 16 kbyte ROM, 384 byte RAM</li> </ul>                                                    |

# **Table 1-1 Features (cont)**

| Item                     | Description                                                                                                                                                                                                                             |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timers                   | Timer A: 8-bit interval timer                                                                                                                                                                                                           |

|                          | Count-up timer with selection of eight internal clock signals divided from the system clock ( $\phi$ )* and four clock signals divided from the subclock ( $\phi$ <sub>SUB</sub> )                                                      |

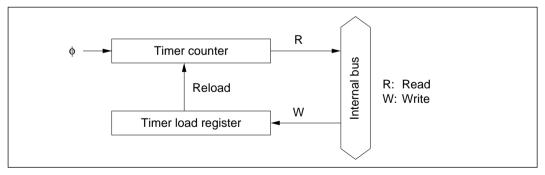

|                          | Timer B: 8-bit reload timer                                                                                                                                                                                                             |

|                          | Count-up timer with selection of seven internal clock signals or event input from pin $\rm P1_0/IRQ_0$                                                                                                                                  |

|                          | Timer C: 8-bit reload timer                                                                                                                                                                                                             |

|                          | Count-up/count-down timer with selection of seven internal clock signals or event input from pin P1 $_1$ /IRQ $_1$                                                                                                                      |

|                          | Timer D: 8-bit event counter                                                                                                                                                                                                            |

|                          | Up-counter for counting input from pin P1 <sub>6</sub> /EVENT                                                                                                                                                                           |

|                          | Timer E: 8-bit reloadable timer                                                                                                                                                                                                         |

|                          | Count-up timer with selection of eight internal clock signals. Square-wave (50% duty cycle) output with a fixed frequency or variable frequency controlled by timer E overflow can be selected by pin P1 $_5$ /IRQ $_5$ /TMOE settings. |

|                          | Note: * φ indicates a clock frequency that is divided in half from the original oscillator frequency                                                                                                                                    |

| 14-bit PWM               | Pulse-division PWM designed for less ripple                                                                                                                                                                                             |

|                          | <ul> <li>Can be used as a 14-bit D/A converter by connecting to an external low-<br/>pass filter</li> </ul>                                                                                                                             |

| VFD<br>driver/controller | <ul> <li>Up to 24 segment pins and up to 16 digit pins (of which 8 are for both<br/>uses)</li> </ul>                                                                                                                                    |

|                          | <ul> <li>Brightness adjustable in 8 steps (dimmer function)</li> </ul>                                                                                                                                                                  |

|                          | <ul> <li>Digit and segment pins can be switched to use as general-purpose high-<br/>voltage pins</li> </ul>                                                                                                                             |

|                          | <ul> <li>Key scan interval can be enabled or disabled</li> </ul>                                                                                                                                                                        |

|                          | <ul> <li>Interrupt can be requested when key scan interval starts</li> </ul>                                                                                                                                                            |

| Serial communica-        | 2-channel synchronous SCI1 and SCI2                                                                                                                                                                                                     |

| tion interface           | Choice of 8-bit or 16-bit data transfer (SCI1)                                                                                                                                                                                          |

|                          | <ul> <li>Automatic transfer of 32-byte data (SCI2)</li> </ul>                                                                                                                                                                           |

|                          | Overrun error detection possible                                                                                                                                                                                                        |

|                          | <ul> <li>Interrupt can be requested when transfer is complete</li> </ul>                                                                                                                                                                |

**Table 1-1 Features (cont)**

| Item                | Description                                         |                                    |                                                             |                                  |  |

|---------------------|-----------------------------------------------------|------------------------------------|-------------------------------------------------------------|----------------------------------|--|

| A/D converter       | Successive approximations using a resistance ladder |                                    |                                                             |                                  |  |

|                     | Resolution: 8 bits                                  | 3                                  |                                                             |                                  |  |

|                     | 8-channel analog                                    | g input port                       |                                                             |                                  |  |

|                     | Conversion time:                                    | 31/\phi or 62/\phi per ch          | annel                                                       |                                  |  |

|                     | • Interrupt can be                                  | requested at compl                 | etion of A/D conv                                           | version                          |  |

| I/O ports           | High-voltage I/O                                    | pins: 32                           |                                                             |                                  |  |

|                     | <ul> <li>High-voltage inpo</li> </ul>               | ut pin: 1                          |                                                             |                                  |  |

|                     | <ul> <li>Standard-voltage</li> </ul>                | e I/O pins: 12                     |                                                             |                                  |  |

|                     | <ul> <li>Standard-voltage</li> </ul>                | e input pins: 9                    |                                                             |                                  |  |

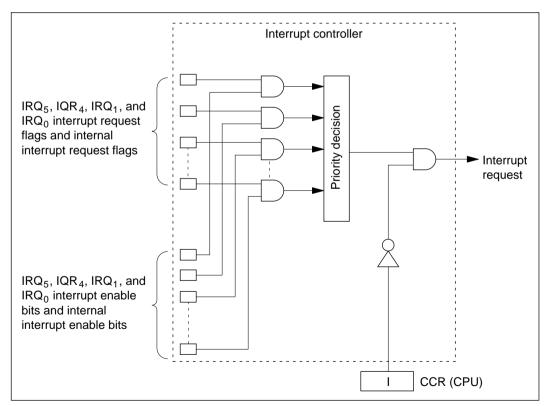

| Interrupts          | Four external into                                  | errupt pins: IRQ <sub>5</sub> , IF | $\overline{RQ_4}$ , $\overline{IRQ_1}$ , $\overline{IRQ_0}$ |                                  |  |

|                     | <ul> <li>Ten internal inter</li> </ul>              | rupt sources                       |                                                             |                                  |  |

| Low power operation | Sleep mode                                          |                                    |                                                             |                                  |  |

| modes               | Standby mode                                        |                                    |                                                             |                                  |  |

|                     | <ul> <li>Watch mode</li> </ul>                      |                                    |                                                             |                                  |  |

|                     | <ul> <li>Subactive mode</li> </ul>                  |                                    |                                                             |                                  |  |

| Other               | <ul> <li>Built-in pulse ger</li> </ul>              | nerators for system                | clock and subclo                                            | ock                              |  |

|                     | • Timer A can run                                   | on the subclock for                | use as a time ba                                            | ase                              |  |

| Product lineup      | Produc                                              | t Code                             |                                                             |                                  |  |

|                     | Mask ROM Version                                    | ZTAT™ Version                      | Package                                                     | ROM/RAM Size                     |  |

|                     | HD6433714H                                          | HD6473714H                         | 64 pin GFP<br>(FP-64A)                                      | ROM: 32 kbytes<br>RAM: 512 bytes |  |

|                     | HD6433714P                                          | HD6473714P                         | 64 pin SDIP<br>(DP-64S)                                     |                                  |  |

|                     | HD6433713H                                          | _                                  | 64 pin QFP<br>(FP-64A)                                      | ROM: 24 kbytes<br>RAM: 384 bytes |  |

|                     | HD6433713P                                          | _                                  | 64 pin SDIP<br>(DP-64S)                                     | -                                |  |

|                     | HD6433712H                                          | _                                  | 64 pin QFP<br>(FP-64A)                                      | ROM: 16 kbytes<br>RAM: 384 bytes |  |

|                     | HD6433712P                                          | _                                  | 64 pin SDIP<br>(DP-64S)                                     |                                  |  |

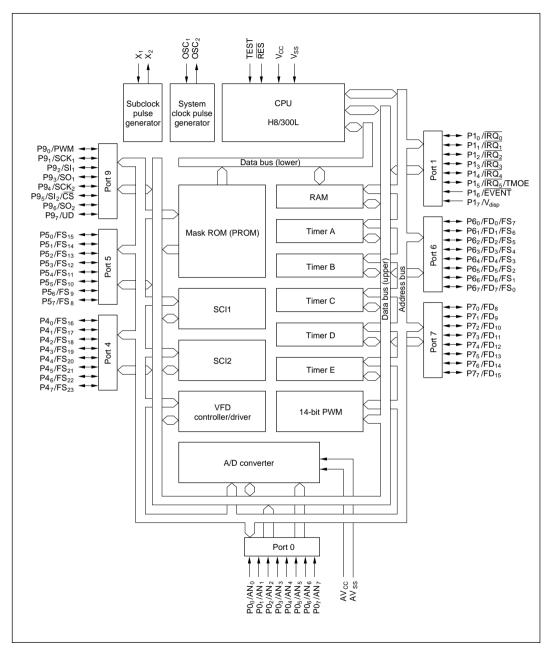

# 1.2 Internal Block Diagram

Figure 1-1 is an internal block diagram of the H8/3714 Series.

Figure 1-1 Block Diagram

# 1.3 Pin Arrangement and Functions

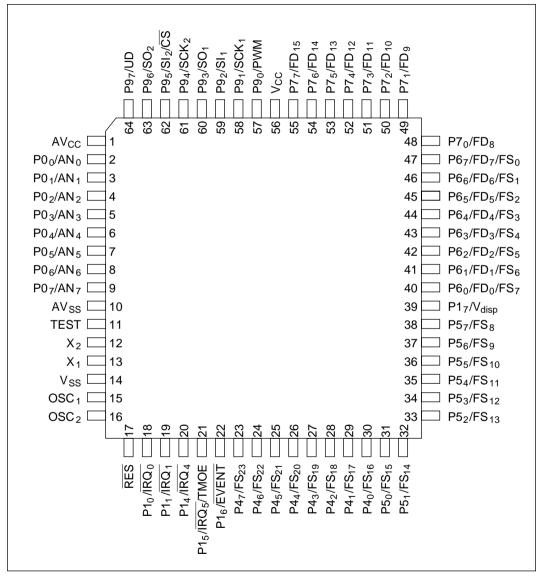

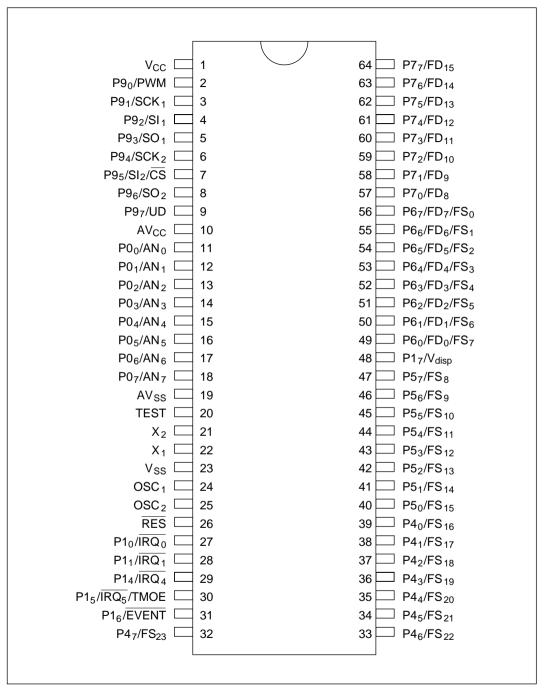

### 1.3.1 Pin Arrangement

The pin arrangements for the H8/3714 Series are shown in figure 1-2 (FP-64A) and figure 1-3 (DP-64S).

Figure 1-2 Pin Arrangement (FP-64A: Top View)

Figure 1-3 Pin Arrangement (DP-64S: Top View)

# 1.3.2 Pin Functions

# 1. List of pin functions

Table 1-2 lists the pin functions of the LSI.

**Table 1-2 List of Pin Functions**

# Pin No.

| FP-64A | P-64A DP-64S Name and Function |                                                                                                    | PROM Mode       |  |

|--------|--------------------------------|----------------------------------------------------------------------------------------------------|-----------------|--|

| 6      | 15                             | P0 <sub>4</sub> /AN <sub>4</sub> (standard input port/analog input channel)                        | NC              |  |

| 7      | 16                             | P0 <sub>5</sub> /AN <sub>5</sub> (standard input port/analog input channel)                        | NC              |  |

| 8      | 17                             | P0 <sub>6</sub> /AN <sub>6</sub> (standard input port/analog input channel)                        | NC              |  |

| 9      | 18                             | P0 <sub>7</sub> /AN <sub>7</sub> (standard input port/analog input channel)                        | NC              |  |

| 10     | 19                             | AV <sub>SS</sub> (reference voltage for A/D converter)                                             | V <sub>SS</sub> |  |

| 11     | 20                             | TEST (test pin)                                                                                    | V <sub>CC</sub> |  |

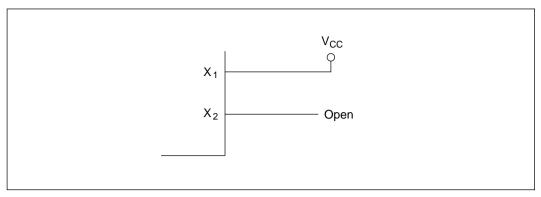

| 12     | 21                             | X <sub>2</sub> (subclock oscillator connection)                                                    | NC              |  |

| 13     | 22                             | X <sub>1</sub> (subclock oscillator connection)                                                    | V <sub>CC</sub> |  |

| 14     | 23                             | V <sub>SS</sub> (ground)                                                                           | V <sub>SS</sub> |  |

| 15     | 24                             | OSC <sub>1</sub> (system clock oscillator connection)                                              | V <sub>SS</sub> |  |

| 16     | 25                             | OSC <sub>2</sub> (system clock oscillator connection)                                              | NC              |  |

| 17     | 26                             | RES (reset input)                                                                                  | V <sub>PP</sub> |  |

| 18     | 27                             | P1 <sub>0</sub> /IRQ <sub>0</sub> (standard I/O port/external interrupt or timer B event input)    | NC              |  |

| 19     | 28                             | P1 <sub>1</sub> /IRQ <sub>1</sub> (standard I/O port/external interrupt or timer C event input)    | NC              |  |

| 20     | 29                             | P1 <sub>4</sub> /IRQ <sub>4</sub> (standard I/O port/external interrupt)                           | NC              |  |

| 21     | 30                             | P1 <sub>5</sub> /IRQ <sub>5</sub> /TMOE (standard I/O port/external interrupt/warning tone output) | NC              |  |

| 22     | 31                             | P1 <sub>6</sub> /EVENT (standard input port/timer D event input)                                   | EA <sub>9</sub> |  |

| 23     | 32                             | P4 <sub>7</sub> /FS <sub>23</sub> (high-voltage I/O port/VFD segment output)                       | NC              |  |

| 24     | 33                             | P4 <sub>6</sub> /FS <sub>22</sub> (high-voltage I/O port/VFD segment output)                       | NC              |  |

| 25     | 34                             | P4 <sub>5</sub> /FS <sub>21</sub> (high-voltage I/O port/VFD segment output)                       | NC              |  |

| 26     | 35                             | P4 <sub>4</sub> /FS <sub>20</sub> (high-voltage I/O port/VFD segment output)                       | NC              |  |

| 27     | 36                             | P4 <sub>3</sub> /FS <sub>19</sub> (high-voltage I/O port/VFD segment output)                       | V <sub>CC</sub> |  |

| 28     | 37                             | P4 <sub>2</sub> /FS <sub>18</sub> (high-voltage I/O port/VFD segment output)                       | V <sub>CC</sub> |  |

| 29     | 38                             | P4 <sub>1</sub> /FS <sub>17</sub> (high-voltage I/O port/VFD segment output)                       | V <sub>SS</sub> |  |

**Table 1-2** List of Pin Functions (cont)

Pin No.

| 110.   |        |                                                                                                    |                  |  |

|--------|--------|----------------------------------------------------------------------------------------------------|------------------|--|

| FP-64A | DP-64S | Name and Function                                                                                  | PROM Mode        |  |

| 30     | 39     | P4 <sub>0</sub> /FS <sub>16</sub> (high-voltage I/O port/VFD segment output)                       | V <sub>SS</sub>  |  |

| 31     | 40     | P5 <sub>0</sub> /FS <sub>15</sub> (high-voltage I/O port/VFD segment output)                       | EA <sub>0</sub>  |  |

| 32     | 41     | P5 <sub>1</sub> /FS <sub>14</sub> (high-voltage I/O port/VFD segment output)                       | EA <sub>1</sub>  |  |

| 33     | 42     | P5 <sub>2</sub> /FS <sub>13</sub> (high-voltage I/O port/VFD segment output)                       | EA <sub>2</sub>  |  |

| 34     | 43     | P5 <sub>3</sub> /FS <sub>12</sub> (high-voltage I/O port/VFD segment output)                       | EA <sub>3</sub>  |  |

| 35     | 44     | P5 <sub>4</sub> /FS <sub>11</sub> (high-voltage I/O port/VFD segment output)                       | EA <sub>4</sub>  |  |

| 36     | 45     | P5 <sub>5</sub> /FS <sub>10</sub> (high-voltage I/O port/VFD segment output)                       | EA <sub>5</sub>  |  |

| 37     | 46     | P5 <sub>6</sub> /FS <sub>9</sub> (high-voltage I/O port/VFD segment output)                        | EA <sub>6</sub>  |  |

| 38     | 47     | P5 <sub>7</sub> /FS <sub>8</sub> (high-voltage I/O port/VFD segment output)                        | EA <sub>7</sub>  |  |

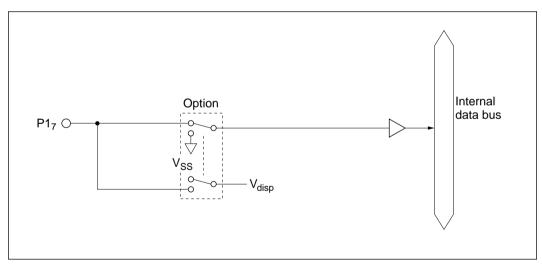

| 39     | 48     | P1 <sub>7</sub> /V <sub>disp</sub> (high-voltage input port/VFD power source)                      | V <sub>CC</sub>  |  |

| 40     | 49     | P6 <sub>0</sub> /FD <sub>0</sub> /FS <sub>7</sub> (high-voltage I/O port/VFD digit-segment output) | NC               |  |

| 41     | 50     | P6 <sub>1</sub> /FD <sub>1</sub> /FS <sub>6</sub> (high-voltage I/O port/VFD digit-segment output) | NC               |  |

| 42     | 51     | P6 <sub>2</sub> /FD <sub>2</sub> /FS <sub>5</sub> (high-voltage I/O port/VFD digit-segment output) | NC               |  |

| 43     | 52     | P6 <sub>3</sub> /FD <sub>3</sub> /FS <sub>4</sub> (high-voltage I/O port/VFD digit-segment output) | NC               |  |

| 44     | 53     | P6 <sub>4</sub> /FD <sub>4</sub> /FS <sub>3</sub> (high-voltage I/O port/VFD digit-segment output) | NC               |  |

| 45     | 54     | P6 <sub>5</sub> /FD <sub>5</sub> /FS <sub>2</sub> (high-voltage I/O port/VFD digit-segment output) | NC               |  |

| 46     | 55     | P6 <sub>6</sub> /FD <sub>6</sub> /FS <sub>1</sub> (high-voltage I/O port/VFD digit-segment output) | NC               |  |

| 47     | 56     | P6 <sub>7</sub> /FD <sub>7</sub> /FS <sub>0</sub> (high-voltage I/O port/VFD digit-segment output) | NC               |  |

| 48     | 57     | P7 <sub>0</sub> /FD <sub>8</sub> (high-voltage I/O port/VFD digit output)                          | EA <sub>8</sub>  |  |

| 49     | 58     | P7 <sub>1</sub> /FD <sub>9</sub> (high-voltage I/O port/VFD digit output)                          | ŌĒ               |  |

| 50     | 59     | P7 <sub>2</sub> /FD <sub>10</sub> (high-voltage I/O port/VFD digit output)                         | EA <sub>10</sub> |  |

**Table 1-2 List of Pin Functions (cont)**

#### Pin No.

| FP-64A | DP-64S | Name and Function                                                                                  | PROM Mode        |

|--------|--------|----------------------------------------------------------------------------------------------------|------------------|

| 51     | 60     | P7 <sub>3</sub> /FD <sub>11</sub> (high-voltage I/O port/VFD digit output)                         | EA <sub>11</sub> |

| 52     | 61     | P7 <sub>4</sub> /FD <sub>12</sub> (high-voltage I/O port/VFD digit output)                         | EA <sub>12</sub> |

| 53     | 62     | P7 <sub>5</sub> /FD <sub>13</sub> (high-voltage I/O port/VFD digit output)                         | EA <sub>13</sub> |

| 54     | 63     | P7 <sub>6</sub> /FD <sub>14</sub> (high-voltage I/O port/VFD digit output)                         | EA <sub>14</sub> |

| 55     | 64     | P7 <sub>7</sub> /FD <sub>15</sub> (high-voltage I/O port/VFD digit output)                         | CE               |

| 56     | 1      | V <sub>CC</sub> (system power source)                                                              | $V_{CC}$         |

| 57     | 2      | P9 <sub>0</sub> /PWM (standard I/O port/PWM output)                                                | EO <sub>0</sub>  |

| 58     | 3      | P9 <sub>1</sub> /SCK <sub>1</sub> (standard I/O port/clock output)                                 | EO <sub>1</sub>  |

| 59     | 4      | P9 <sub>2</sub> /SI <sub>1</sub> (standard I/O port/data input)                                    | EO <sub>2</sub>  |

| 60     | 5      | P9 <sub>3</sub> /SO <sub>1</sub> (standard I/O port/data output)                                   | EO <sub>3</sub>  |

| 61     | 6      | P9 <sub>4</sub> /SCK <sub>2</sub> (standard I/O port/clock I/O)                                    | EO <sub>4</sub>  |

| 62     | 7      | P9 <sub>5</sub> /SI <sub>2</sub> / <del>CS</del> (standard I/O port/data input/chip select output) | EO <sub>5</sub>  |

| 63     | 8      | P9 <sub>6</sub> /SO <sub>2</sub> (standard I/O port/data output)                                   | EO <sub>6</sub>  |

| 64     | 9      | P9 <sub>7</sub> /UD (standard I/O port/timer C up-down control)                                    | EO <sub>7</sub>  |

| 1      | 10     | AV <sub>CC</sub> (reference power source for A/D converter)                                        | V <sub>CC</sub>  |

| 2      | 11     | PO <sub>0</sub> /AN <sub>0</sub> (standard input port/analog input channel)                        | NC               |

| 3      | 12     | PO <sub>1</sub> /AN <sub>1</sub> (standard input port/analog input channel)                        | NC               |

| 4      | 13     | PO <sub>2</sub> /AN <sub>2</sub> (standard input port/analog input channel)                        | NC               |

| 5      | 14     | PO <sub>3</sub> /AN <sub>3</sub> (standard input port/analog input channel)                        | NC               |

Notes: 1. NC pins should be left unconnected.

2. Details on PROM mode are given in 4.2, PROM Mode.

# 2. Pin functions

Table 1-3 explains the functions of each pin in more detail.

**Table 1-3 Pin Functions**

|                   |                   | Pin No. |        |        |                                                                                                                                                                            |  |

|-------------------|-------------------|---------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Туре              | Symbol            | FP-64A  | DP-64S | I/O    | Name and Functions                                                                                                                                                         |  |

| Power supply pins | $V_{CC}$          | 56      | 1      | Input  | <b>Power source:</b> Connects to a power supply (+5 V)                                                                                                                     |  |

|                   |                   |         |        |        | All $V_{CC}$ pins should be connected to the system power supply (+5 V).                                                                                                   |  |

|                   | $V_{SS}$          | 14      | 23     | Input  | <b>Ground:</b> Connects to a power supply (0 V).                                                                                                                           |  |

|                   |                   |         |        |        | All $V_{SS}$ pins should be connected to the system power supply (0 V).                                                                                                    |  |

|                   | AV <sub>CC</sub>  | 1       | 10     | Input  | Analog power supply: This is the reference power supply pin for the A/D converter. When the A/D converter is not used, connect this pin to the system power supply (+5 V). |  |

|                   | $AV_SS$           | 10      | 19     | Input  | Analog ground: This is the A/D converter ground pin. It should be connected to the system power supply (0 V).                                                              |  |

|                   | V <sub>disp</sub> | 39      | 48     | Input  | <b>VFD power supply:</b> This pin should be connected to a VFD driver power supply.                                                                                        |  |

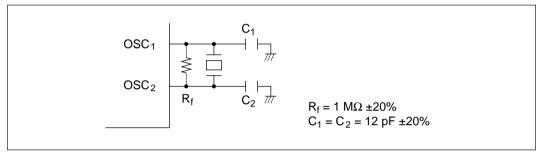

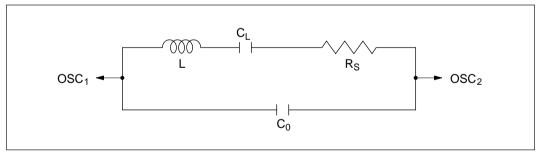

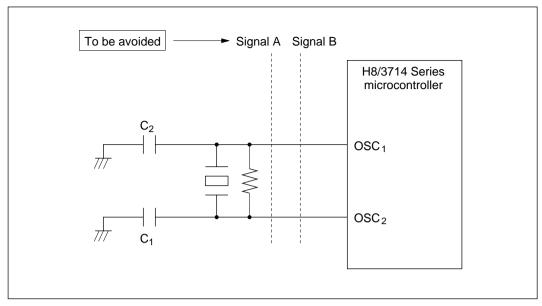

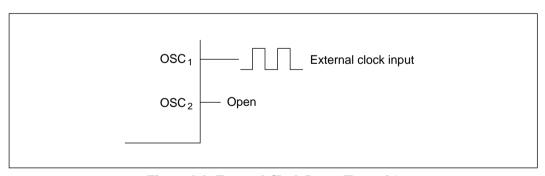

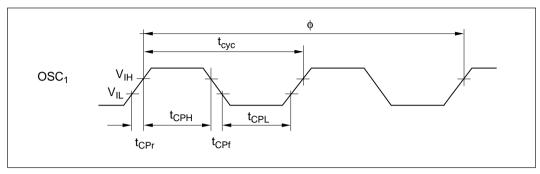

| Clock pins        | OSC <sub>1</sub>  | 15      | 24     | Input  | This pin connects to a crystal or ceramic oscillator, or can be used to input an external clock.                                                                           |  |

|                   |                   |         |        |        | See section 6, Clock Pulse Generators, for a typical connection diagram.                                                                                                   |  |

|                   | OSC <sub>2</sub>  | 16      | 25     | Output | This pin connects to a crystal or ceramic oscillator.                                                                                                                      |  |

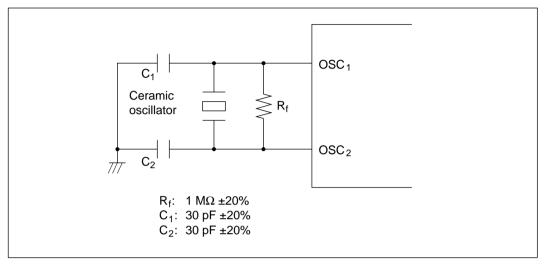

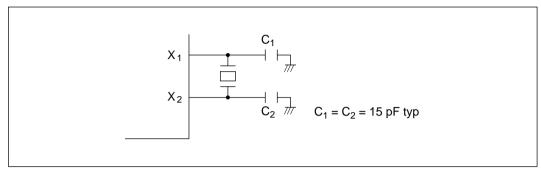

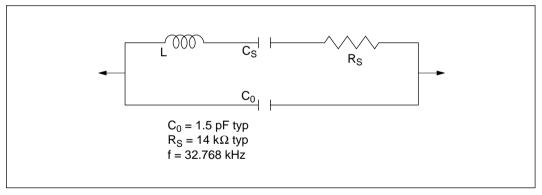

|                   | X <sub>1</sub>    | 13      | 22     | Input  | This pin connects to a 32.768 kHz crystal oscillator.                                                                                                                      |  |

|                   |                   |         |        |        | For a typical connection diagram, see section 6, Clock Pulse Generators.                                                                                                   |  |

|                   | X <sub>2</sub>    | 12      | 21     | Output | This pin connects to a 32.768 kHz crystal oscillator.                                                                                                                      |  |

**Table 1-3 Pin Functions (cont)**

|                |                  | Pin No. |        |       |                                                                                                                                                                                               |  |

|----------------|------------------|---------|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Туре           | Symbol           | FP-64A  | DP-64S | 1/0   | Name and Functions                                                                                                                                                                            |  |

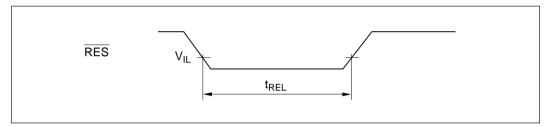

| System control | RES              | 17      | 26     | Input | <b>Reset:</b> When this pin goes to low level, the chip is reset.                                                                                                                             |  |

|                | TEST             | 11      | 20     | Input | <b>Test:</b> This pin is not for use in application systems. It should be connected to V <sub>SS</sub> .                                                                                      |  |

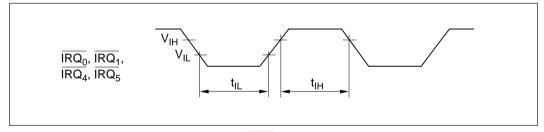

| Interrupt pins | ĪRQ <sub>0</sub> | 18      | 27     | Input | <b>External interrupt request 0:</b> This is an input pin for external interrupts for which there is a choice between rising and falling edge sensing. It can be used to exit low-power mode. |  |

|                |                  |         |        |       | This pin can be used as the event input pin for timer B. A noise cancel function is also provided.                                                                                            |  |

|                | ĪRQ <sub>1</sub> | 19      | 28     | Input | External interrupt request 1: This is an input pin for external interrupts for which there is a choice between rising and falling edge sensing. It can be used to exit low-power mode.        |  |

|                |                  |         |        |       | This pin can be used as the event input pin for timer C.                                                                                                                                      |  |

|                | ĪRQ <sub>4</sub> | 20      | 29     | Input | <b>External interrupt request 4:</b> This is an input pin for external interrupts for which there is a choice between rising and falling edge sensing.                                        |  |

|                | ĪRQ <sub>5</sub> | 21      | 30     | Input | <b>External interrupt request 5:</b> This is an input pin for external interrupts that are detected at the falling edge.                                                                      |  |

**Table 1-3 Pin Functions (cont)**

|                         |                                      | Pin No.  |        |        |                                                                                                                                                                              |  |

|-------------------------|--------------------------------------|----------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Туре                    | Symbol                               | FP-64A   | DP-64S | 1/0    | Name and Functions                                                                                                                                                           |  |

| Timer pins              | ĪRQ <sub>0</sub>                     | 18       | 27     | Input  | <b>Timer B event counter input:</b> This is an event input pin for input to the timer B counter.                                                                             |  |

|                         | ĪRQ <sub>1</sub>                     | 19       | 28     | Input  | <b>Timer C event counter input:</b> This is an event input pin for input to the timer C counter.                                                                             |  |

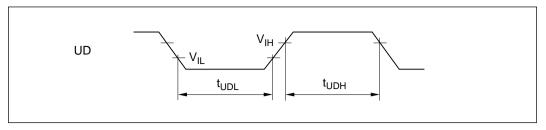

|                         | UD                                   | 64       | 9      | Input  | Timer C up/down select: This pin selects whether the timer C counter is used for up- or down-counting. At high level it selects down-counting, and at low level up-counting. |  |

|                         |                                      |          |        |        | Input to this pin is valid only when bit TMC6 in timer mode register C (TMC) is set to 1.                                                                                    |  |

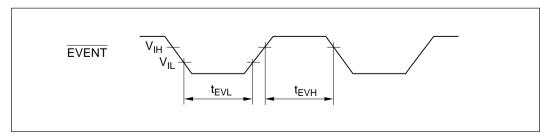

|                         | EVENT                                | 22       | 31     | Input  | <b>Timer D event counter input:</b> This is an event input pin for input to the timer D counter.                                                                             |  |

|                         | TMOE                                 | 21       | 30     | Output | <b>Timer E output:</b> This is an output pin for waveforms generated by the timer E output circuit.                                                                          |  |

| 14-bit PWM pin          | PWM                                  | 57       | 2      | Output | <b>14-bit PWM output:</b> This is an output pin for waveforms generated by the 14-bit PWM.                                                                                   |  |

| Serial communication    | SO <sub>1</sub><br>SO <sub>2</sub>   | 60<br>63 | 5<br>8 | Output | Serial transmit data output (channels 1 and 2): These are SCI data output pins.                                                                                              |  |

| interface (SCI)<br>pins | SI <sub>1</sub><br>SI <sub>2</sub>   | 59<br>62 | 4<br>7 | Input  | Serial receive data input (channels 1 and 2): These are SCI data input pins.                                                                                                 |  |

|                         | SCK <sub>1</sub><br>SCK <sub>2</sub> | 58<br>61 | 3<br>6 | I/O    | Serial clock I/O (channels 1 and 2):<br>These are SCI clock I/O pins.                                                                                                        |  |

|                         | CS                                   | 62       | 7      | Output | Chip select output: When SCI2 is in transmit mode and the serial clock is an internal clock, this pin goes low.                                                              |  |

|                         |                                      |          |        |        | This function is valid when bit SI2 in port mode register 2 (PMR2) is 1 and the CS bit in PMR3 is 1.                                                                         |  |

**Table 1-3 Pin Functions (cont)**

|                           |                                                                          | Pin No.  |                      |        |                                                                                                                                                                    |

|---------------------------|--------------------------------------------------------------------------|----------|----------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре                      | Symbol                                                                   | FP-64A   | DP-64S               | 1/0    | Name and Functions                                                                                                                                                 |

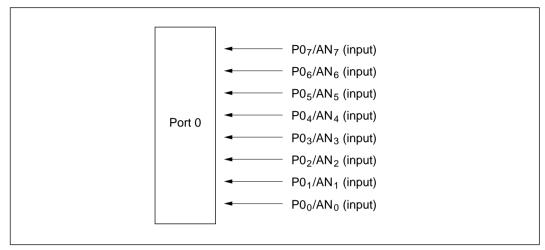

| I/O ports                 | P0 <sub>7</sub> to P0 <sub>0</sub>                                       | 9 to 2   | 18 to 11             | Input  | Port 0: This is an 8-bit input port.                                                                                                                               |

|                           | P1 <sub>7</sub>                                                          | 39       | 48                   | Input  | Port 1 (bit 7): This is a 1-bit high-voltage input pin.                                                                                                            |

|                           | P1 <sub>6</sub>                                                          | 22       | 31                   | Input  | Port 1 (bit 6): This is a 1-bit input pin.                                                                                                                         |

|                           | P1 <sub>5</sub> , P1 <sub>4</sub> ,<br>P1 <sub>1</sub> , P1 <sub>0</sub> | 21 to 18 | 30 to 27             | I/O    | Port 1: This is a 4-bit group of I/O pins. Input or output can be designated for each bit by means of port control register 1 (PCR1).                              |

|                           | P4 <sub>7</sub> to P4 <sub>0</sub>                                       | 23 to 30 | 32 to 39             | I/O    | Port 4: This is an 8-bit high-voltage I/O port.                                                                                                                    |

|                           | P5 <sub>7</sub> to<br>P5 <sub>0</sub>                                    | 38 to 31 | 47 to 40             | I/O    | <b>Port 5:</b> This is an 8-bit high-voltage I/O port.                                                                                                             |

|                           | P6 <sub>7</sub> to P6 <sub>0</sub>                                       | 47 to 40 | 56 to 49             | I/O    | <b>Port 6:</b> This is an 8-bit high-voltage I/O port.                                                                                                             |

|                           | P7 <sub>7</sub> to P7 <sub>0</sub>                                       | 55 to 48 | 64 to 57             | I/O    | <b>Port 7:</b> This is an 8-bit high-voltage I/O port.                                                                                                             |

|                           | P9 <sub>7</sub> to                                                       | 64 to 57 | 9 to 2               | I/O    | <b>Port 9:</b> This is an 8-bit I/O port. Input or output can be designated for each bit by means of PCR9.                                                         |

| A/D converter             | AN <sub>7</sub> to<br>AN <sub>0</sub>                                    | 9 to 2   | 18 to 11             | Input  | Analog input channels 7 to 0: These are analog data input channels to the A/D converter.                                                                           |

| VFD controller/<br>driver | FD <sub>15</sub> to<br>FD <sub>0</sub>                                   | 55 to 40 | 64 to 49             | Output | <b>VFD digit output:</b> These are digit output pins from the VFD controller/driver.                                                                               |

|                           | FS <sub>23</sub> to<br>FS <sub>8</sub>                                   |          | 32 to 47<br>49 to 56 | I/O    | VFD segment output: These are segment output pins from the VFD                                                                                                     |

|                           | FS <sub>7</sub> to<br>FS <sub>0</sub>                                    |          |                      |        | controller/driver. When a key scan interval is set during display operations, these pins can be used by the CPU during this interval as general-purpose I/O ports. |

# Section 2 CPU

#### 2.1 Overview

The H8/300L CPU has sixteen 8-bit general registers, which can also be paired as eight 16-bit registers. Its concise, optimized instruction set is designed for high-speed operation.

#### 2.1.1 Features

The main features of the H8/300L CPU are listed below.

- · General-register architecture

- Sixteen 8-bit general registers, also usable as eight 16-bit general registers

- Instruction set with 55 basic instructions, including:

- Multiply and divide instructions

- Powerful bit-manipulation instructions

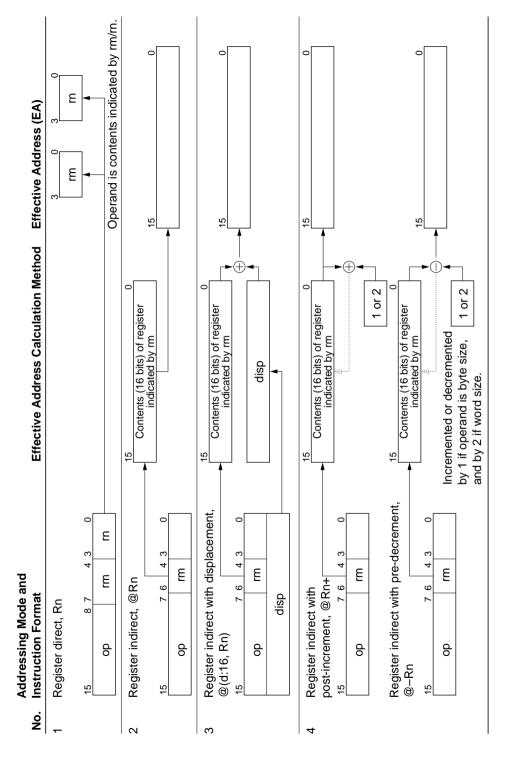

- Eight addressing modes

| <ul> <li>Register direct</li> </ul>                                        | Rn              |

|----------------------------------------------------------------------------|-----------------|

| <ul> <li>Register indirect</li> </ul>                                      | @Rn             |

| <ul> <li>Register indirect with displacement</li> </ul>                    | @(d:16, Rn)     |

| <ul> <li>Register indirect with post-increment or pre-decrement</li> </ul> | @Rn+ or @-Rn    |

| <ul> <li>Absolute address</li> </ul>                                       | @aa:8 or @aa:16 |

| — Immediate                                                                | #xx:8 or #xx:16 |

| <ul> <li>Program-counter relative</li> </ul>                               | @(d:8, PC)      |

| <ul> <li>Memory indirect</li> </ul>                                        | @@aa:8          |

- 64-kbyte address space

- High-speed operation

- All frequently used instructions are executed in two to four states

- High-speed arithmetic and logic operations

- 8- or 16-bit register-register add or subtract: 0.5 μs\* 8 × 8-bit multiply: 3.5 μs\* 16 ÷ 8-bit divide: 3.5 μs\*

- Low-power operation modes

- SLEEP instruction for transfer to low-power operation

Note: \* These values are at  $\phi = 4$  MHz.

#### 2.1.2 Address Space

The H8/300L CPU supports an address space of up to 64 kbytes for storing program code and data.

The memory map varies with the ROM size. Figure 2-1 gives memory map.

Figure 2-1 Memory Map

# 2.1.3 Register Configuration

Figure 2-2 shows the register structure of the H8/300L CPU. There are two groups of registers: the general registers and control registers.

Figure 2-2 CPU Registers

# 2.2 Register Descriptions

#### 2.2.1 General Registers

All the general registers can be used as both data registers and address registers.

When used as data registers, they can be accessed as 16-bit registers (R0 to R7), or the high bytes (R0H to R7H) and low bytes (R0L to R7L) can be accessed separately as 8-bit registers.

When used as address registers, the general registers are accessed as 16-bit registers (R0 to R7).

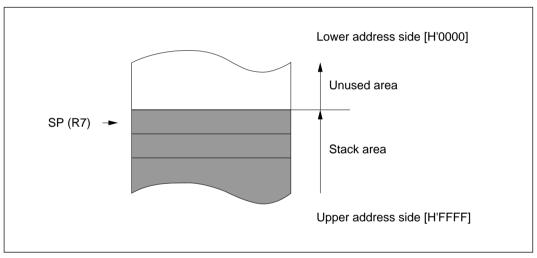

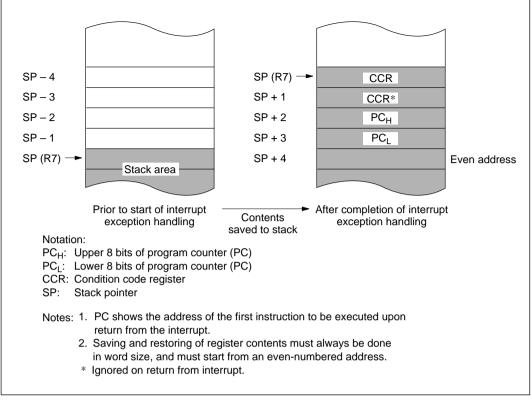

R7 also functions as the stack pointer (SP), used implicitly by hardware in exception processing and subroutine calls. When it functions as the stack pointer, as indicated in figure 2-3, SP (R7) points to the top of the stack.

Figure 2-3 Stack Pointer

#### 2.2.2 Control Registers

The CPU control registers include a 16-bit program counter (PC) and an 8-bit condition code register (CCR).

- 1. **Program Counter (PC):** This 16-bit register indicates the address of the next instruction the CPU will execute. All instructions are fetched 16 bits (1 word) at a time, so the least significant bit of the PC is ignored (always regarded as 0).

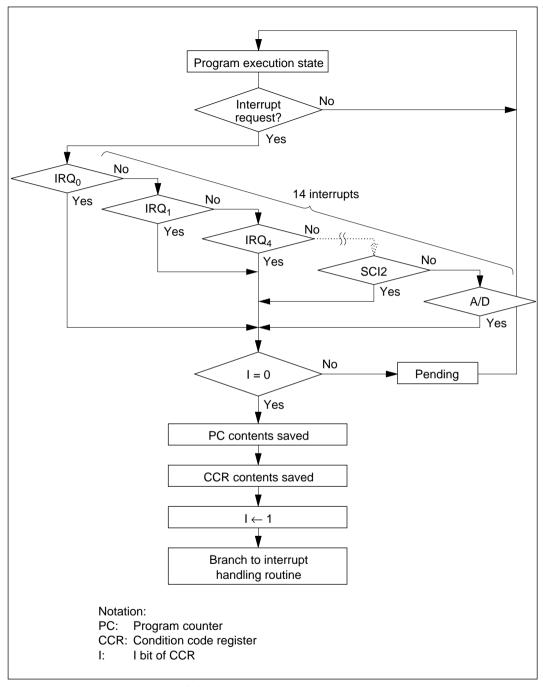

- 2. Condition Code Register (CCR): This 8-bit register contains internal status information, including the interrupt mask bit (I) and half-carry (H), negative (N), zero (Z), overflow (V), and carry (C) flags.

**Bit 7—Interrupt Mask Bit (I):** When this bit is set to 1, interrupts are masked. This bit is set to 1 automatically at the start of exception handling. The interrupt mask bit may be read and written by software. For further details, see 3.2.2, Interrupts.

**Bit 6—User Bit (U):** Can be written and read by software (using the LDC, STC, ANDC, ORC, and XORC instructions).

**Bit 5—Half-Carry Flag (H):** When the ADD.B, ADDX.B, SUB.B, SUBX.B, CMP.B, or NEG.B instruction is executed, this flag is set to 1 if there is a carry or borrow at bit 3, and is cleared to 0 otherwise.

The H flag is used implicitly by the DAA and DAS instructions.

When the ADD.W, SUB.W, or CMP.W instruction is executed, the H flag is set to 1 if there is a carry or borrow at bit 11, and is cleared to 0 otherwise.

**Bit 4—User Bit (U):** Can be written and read by software (using the LDC, STC, ANDC, ORC, and XORC instructions).

**Bit 3—Negative Flag (N):** Indicates the most significant bit (sign bit) of the result of an instruction.

Bit 2—Zero Flag (Z): Set to 1 to indicate zero data, and cleared to 0 to indicate non-zero data.

**Bit 1—Overflow Flag (V):** Set to 1 when an arithmetic overflow occurs, and cleared to 0 at other times.

Bit 0—Carry Flag (C): Set to 1 when a carry occurs, and cleared to 0 otherwise. Used by:

- Add instructions, to indicate a carry

- Subtract instructions, to indicate a borrow

- Shift and rotate instructions, to store the value shifted out of the end bit

The carry flag is also used as a bit accumulator by bit manipulation instructions.

Some instructions leave some or all of the flag bits unchanged. The LDC, STC, ANDC, ORC, and XORC instructions enable the CPU to load and store the CCR, and to set or clear selected bits by logic operations. The N, Z, V, and C flags are used as branching conditions for conditional branching (Bcc) instructions.

Refer to the H8/300L Series Programming Manual for the action of each instruction on the flag bits.

#### 2.2.3 Initial Register Values

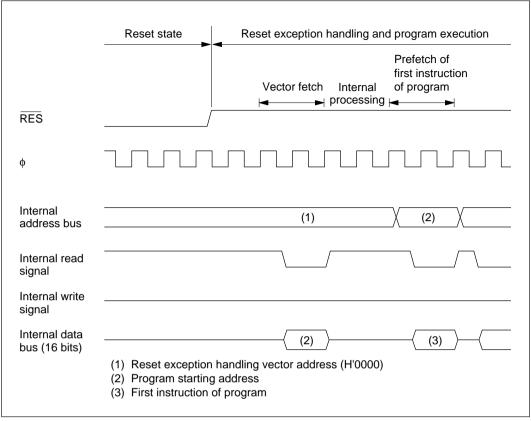

When the CPU is reset, the program counter (PC) is initialized to the value stored at address H'0000 in the vector table, and the I bit in the CCR is set to 1. The other CCR bits and the general registers are not initialized. In particular, the stack pointer (R7) is not initialized. To prevent program crashes the stack pointer should be initialized by software, by the first instruction executed after a reset.

#### 2.3 Data Formats

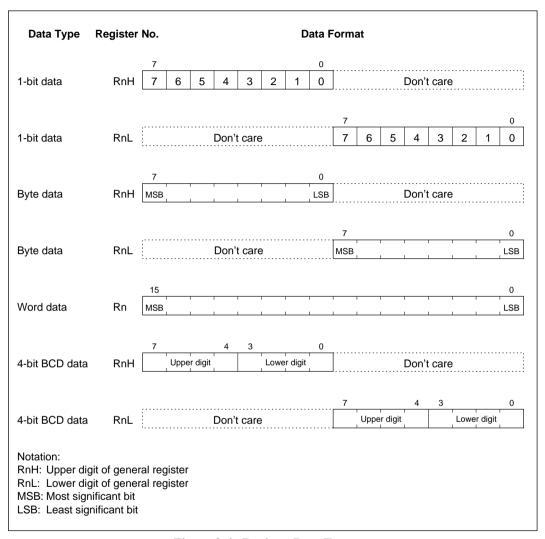

The H8/300L CPU can process 1-bit data, 4-bit (BCD) data, 8-bit (byte) data, and 16-bit (word) data.

- Bit manipulation instructions operate on 1-bit data specified as bit n in a byte operand (n = 0, 1, 2, ..., 7).

- All arithmetic and logic instructions except ADDS and SUBS can operate on byte data.

- The MOV.W, ADD.W, SUB.W, CMP.W, ADDS, SUBS, MULXU (8 bits × 8 bits), and DIVXU (16 bits ÷ 8 bits) instructions operate on word data.

- The DAA and DAS instructions perform decimal arithmetic adjustments on byte data in packed BCD form. Each nibble of the byte is treated as a decimal digit.

# 2.3.1 Data Formats in General Registers

Data of all the sizes above can be stored in general registers as shown in figure 2-4.

Figure 2-4 Register Data Formats

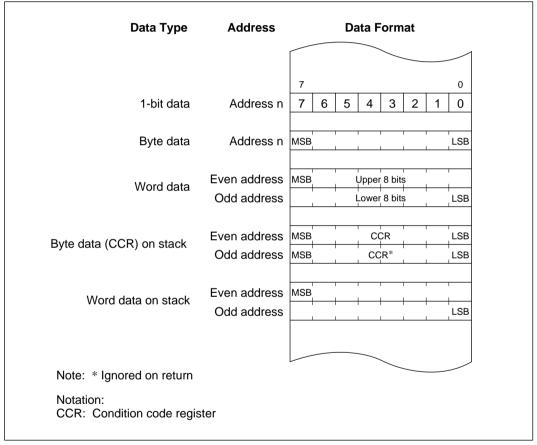

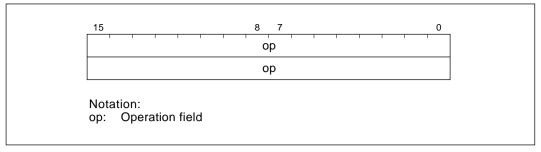

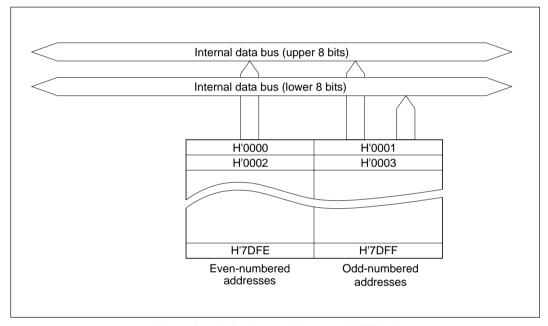

#### 2.3.2 Memory Data Formats